有些设计师有时会忽略设计出来的芯片是否能够顺利的被制造出来应用到产品中,他们往往更关注指标是否达到,先考虑设计再考虑测试,但随着电路复杂程度的提高,这种方法既费时又费力,并且往往造成制造过程中的一些不可预见的测试问题。解决芯片测试的根本方法是在芯片设计时就充分考虑到测试的要求,即在设计阶段就开始考虑如何对电路进行测试,并将一些可测性技术引入到芯片中,以降低测试方法的复杂性,这就是可测性设计(DFT,Design For Testability )。

可测性设计是在满足芯片正常功能的基础上,通过有效地加入测试电路,来降低芯片的测试难度,降低测试成本。同时,可测性并不是指产品可测或不可测,而是度量产品测试难易度的概念,因此一般来说,一切考虑了测试要求的设计,或者说一切能使测试生成和故障诊断变得比较容易的设计都可称为可测性设计。

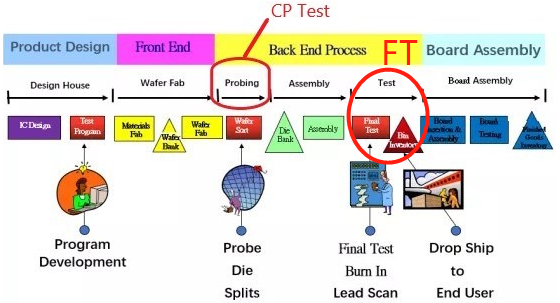

1、CP测试和FT测试

芯片在生产过程中主要有两次测试:CP测试(晶圆测试,Chip Probing)和FT测试(Final Test )。CP是对wafer进行测试,检查fab厂制造的工艺水平

FT是对package进行测试,检查封装厂的制造水平

图1.1 CP和FT测试在芯片制程中的位置

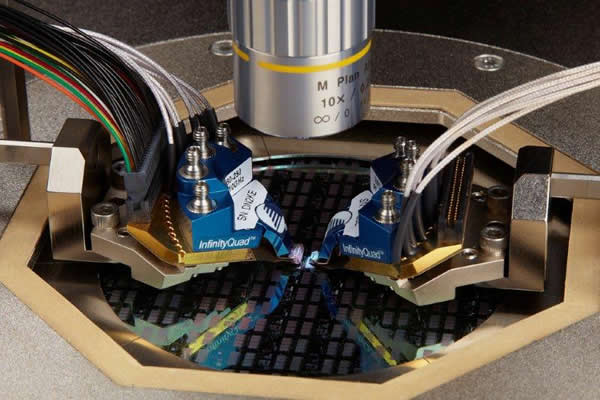

第一次测试是在晶圆加工完成后,测试设备通过探针压到芯片的焊盘(Bonding Pad)上,这叫做CP测试,CP测试一般只做简单的测试,比如电气连通性、电流测试和一些专门为工艺调试的电路参数测试等,如果结果与预计的相同则为合格,否则判定测试失败,在失败芯片上打上标记,往后就不做这些故障芯片的封装和后续加工。

第二次测试是在封装完成后,测试仪通过测试程序完成对芯片的FT测试,这一次的测试一般要求更加严格,要尽可能地检测出有故障的芯片。芯片的FT测试的内容不光是检测故障,还有许多方面需要测试,如功耗、电流、可靠性、工作频率、能够工作的环境温度等。如果检测出芯片有故障,不能通过测试,那么要根据情况做故障分析或失效分析。一般来说故障分析会占用大量的人力、物力和时间,所以一般只是在非常必要的情况下才会去做。对于代工厂来说一些基本的工艺参数如果与预期不一致的话,是必须做分析的,并且要调整生产线,直到工艺稳定,总体偏差越小越好。对于设计者来说,实验性的芯片如果有故障,要多花时间和精力进行详细的调试和分析,找到问题的所在,修改设计直到正确无误。

2、可测性设计的目标

对电路进行可测性设计主要为了达到以下目标:

(1)减少冗余逻辑:冗余逻辑会增加测试生成的复杂性;(2)增加电路的可控制性和可观测性:增加电路的可控性和可观性是提高电路可测性的根本措施;

(3)为了测试而附加的电路对原来电路的性能影响尽可能小:可测性设计都会增加额外的测试电路,通常会使芯片面积增加,影响电路本来的性能;

(4)使测试向量的生成更容易:简单有效的测试向量可以提高测试效率,减少测试成本,尤其是时间成本;

(5)提高测试集的测试质量:提高故障覆盖率、减少测试向量、减少测试时间等。

良好的可测性电路应具有以下特征:

(1)电路容易置于理想的初始状态;(2)电路的任意内部状态很容易通过对原始输入施加测试图形来控制;

(3)通过电路的原始输出或专门的测试点,电路内部的状态可以唯一确认。

3、可测性设计方法

对于频率较高的射频芯片来说,一般只能通过增加芯片内部的控制点和观察点来实现可测性设计,即在电路设计和版图设计的时候,通过增加可探测的电路支点和物理触点来实现芯片可测量,有针对性的对电路的易失效点进行测试测量。

DFT设计针对的对象是什么?

DFT需要处理芯片上所有DC、AC测试需求,即DFT需要涵盖以下电路模块的测量:片上存储器

模拟模块 (如锁相环,LDO,IDV等)

系统控制模块(如串并转换、休眠电路、看门狗电路等)

电源管理模块(如DCDC、LDO等)

寄存器(如ROM、SPI协议等)

放大器(如MOS管、FET管)

DFT基本参与了所有的芯片功能,需要提供芯片初始化时FUSE的管理;需要设计协调时钟、复位,放大器的DC/IV曲线;除此之外,芯片中功能模块的每一个寄存器都是DFT设计的工作对象。

DFT应该参与到芯片支撑的哪些步骤中?

在芯片的整个制程中,都应该有DFT参与的痕迹,也就是DFT至少应该参与到以下过程中:在产品立项阶段就应该定义好DFT的架构

在芯片design阶段应该DFT的逻辑和验证

在封装阶段应保证封装芯片能够完全的表现芯片的功能、逻辑、性能

在可靠性试验阶段应该做到DFT能够实时监控

在交付阶段保证DFT能够为客户提供帮助

在产品生命周期中DFT能够监控寿命

粤公网安备 44030902003195号

粤公网安备 44030902003195号