导语

在低频时,一段普通导线就可以有效地将两个电路短接在一起,但是在高频时候就不同了。在高频电路中,一个小小的过孔、连接器就会对信号产生很大的影响。为了分析高速信号,引入了一个新的模型——传输线。理想传输线的两个主要特征就是时延和阻抗。如果电路中传输线的阻抗突变会导致信号的反射,使得信号质量产生较大的影响,这篇文章主要介绍这方面的信息。

1、集总参数和分布参数

在信号速率比较低的时候,我们通常会把电路等效成电阻、电容以及电感进行分析,这就是我们常说的集总参数电路,和集总参数电路对应的叫做分布参数电路。

集总参数电路和我们中学物理里面的“质点”的概念类似,我们在分析它们的时候可以不考虑自身的大小,而分布参数电路则需要考虑它们自身尺寸对信号的影响。

集总参数和分布参数的区分并没有完全明确的定义,一般我们认为:

满足信号的波长λ>> 器件的尺寸d的时候,我们可以把电路当作是集总参数电路。

不满足信号的波长λ>> 器件的尺寸d的时候,我们可以把电路当作是分布参数电路。

在Howard.Johnson的《高速数字设计》中给出了这样的定义——“如果连线长度小于上升沿有效长度的1/6,则该电路主要表现为一个集总系统的特征”。不过这里的1/6也是个经验参数,也有的作者采用的的是1/4或者 。

。

举一个例子吧,对于我们常用到的51单片机,它们的IO口进行一次数据切换的时间大概在1µs,对应的基波波长约为300m(我们可以近似认为信号在PCB上的传播速度为光速的一半),我们的电路板以及cable的长度一般不会超过3m,和信号的波长比起来尺寸可以忽略不计,所以对于单片机这个级别的系统,我们可以认为它是集总系统。

对于一个速率为480Mbps的USB2.0信号,上升时间大约在0.6ns左右,在上升时间内在PCB上能够传输的距离约为9cm,当器件或者走线的尺寸超过1.5cm的时候,我们就必须考虑它们本身大小对信号带来的影响。

我们使用的USB线就属于分布参数电路,我们一般称之为“传输线”。

2、理想传输线

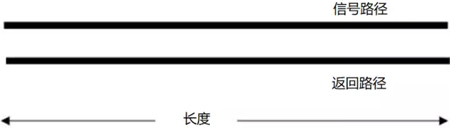

传输线就指的是有长度的两根导线,如下图所示;所谓的有长度,就是指我们无法忽略导线长度对信号带来的影响。

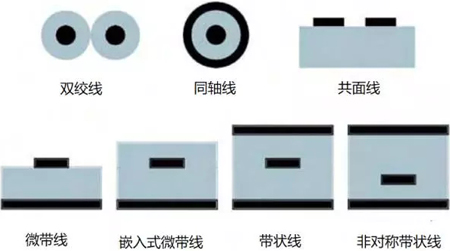

常见的传输线有以下几种:

双绞线,我们平时用的RJ45口的网线就属于双绞线

同轴线,常见的射频电缆一般都属于同轴线,如BNC线

微带线,一般的PCB表层高速走线都是属于微带线

带状线,一般的PCB内层高速走线都是属于带状线。

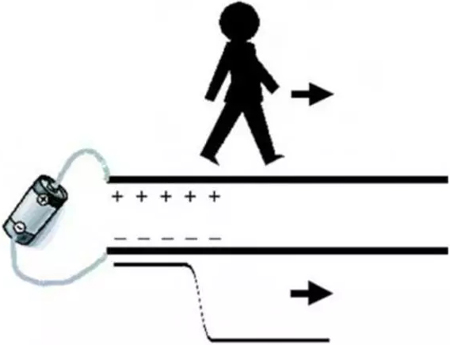

假设有一段足够长的导线,我们把自己当作一个快速上升沿信号,在以15cm/ns的速度穿过这段导线,因为传输线本身可以看作是一个大的电容,信号在经过这段传输线的时候会感受到瞬时电抗的存在。通常把这个感受到的电抗叫做传输线在某个位置的瞬时阻抗,如果在某个位置的电容偏大的话,这个位置的瞬时阻抗也就越小。

如果这条传输线是一条均匀的传输线,它在每一个位置的瞬时阻抗都是相同的,我们把这个固定的阻抗值叫做传输线的特征阻抗,关于传输线的更多内容,可以参考Eric.Bogatin的著作《信号完整性分析》第7章。

我们经常提到的100Ω差分线,其实指的就是这对差分传输线的特征阻抗是100Ω。对于理想传输线而言,它有两个重要的参数:一个是时延,另一个就是它的特征阻抗。

3、传输线的反射

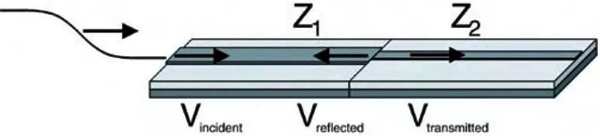

信号在传输的过程中如果遇到阻抗突变,就会产生反射,反射电压的大小和入射电压以及传输线的阻抗有关,如下图所示,假设传输线第一个区域的瞬时阻抗为Z1,第二个区域的瞬时阻抗为Z2。

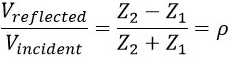

那么反射电压Vreflected和入射电压Vincident满足以下关系:

其中,ρ是我们所关心的反射系数,即反射电压与入射电压的比值,当信号从高阻抗区域进入低阻抗区域时,反射系数的值是负的,当信号从低阻抗区域进入高阻抗区域时,反射系数是正的。反射系数的取值范围是[-1,1]。

相应的,传导系数t满足以下关系:

因为传输线本身有长度,也有瞬时阻抗,如果传输线上有多个点的阻抗不连续,可能会导致多次反射。

4、传输线的多次反射

传输线的反射是很多信号完整性问题的根源,我们见到的很多现象,例如振铃、回沟以及“花生眼”等现象都是由于信号在链路中多次反射造成的。

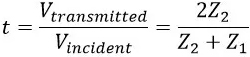

下图是一个振铃现象产生的示例,信号源的内阻为10Ω,往外发送一个上升时间为1ns、幅值为1V的阶跃信号,经过一段15cm的50Ω传输线,在传输线末端开路测量。很容易得到,在传输线两侧的反射系数分别为-0.667和1,传输线末端的信号幅值如下所示。

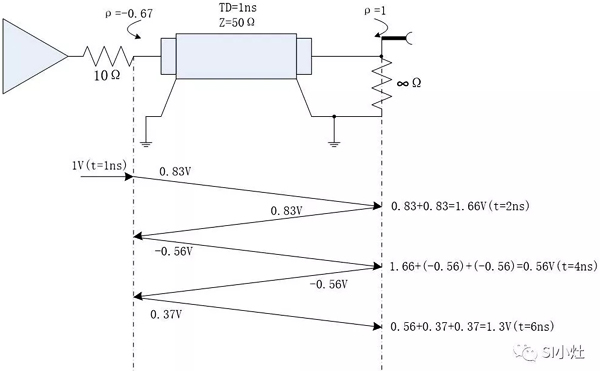

下图是使用TI-TINA仿真得到的结果,和我们上面推算的结果一致,这个就是我们在测试的时候经常能够见到的振铃现象。

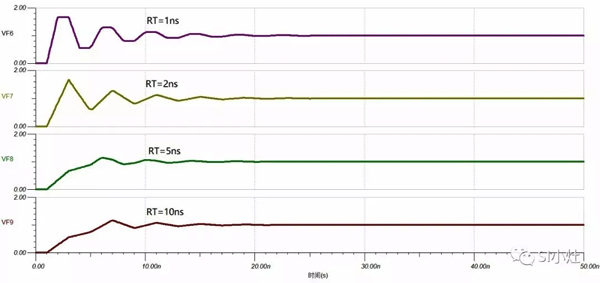

当我们改变输入信号的上升时间,从1ns到10ns,传输线末端的信号如下图所示。从图中我们可以得知,信号上升时间越缓,受到反射的影响越小。当阻抗不连续点的时延小于信号上升时间的1/5的时候,对信号的影响较小。

大家看到这个1/5,是不是想到了些什么?我们在文章的一开始说过,当器件的尺寸小于信号上升时间的1/6(也有的说是1/4)的时候,我们可以忽略器件的自身大小。既然传输线本身的时延可以忽略,那么也就不会存在多次反射了。关于传输线反射的更多内容,可以参考Eric.Bogation的著作《信号完整性分析》第8章内容。

在高速信号的layout中,我们有时候会碰到一些不可避免的阻抗不连续点,例如过孔、连接器以及芯片的封装。如果这些不连续点的自身尺寸较小,而信号的速率又不是特别高的情况下,阻抗不连续造成的影响会比较小。

5、阻抗测量

测量传输线的阻抗需要用到TDR,TDR(Time Domain Reflectometer),TDR的示意图如下图所示,它是由一个高速阶跃信号发生器和采样示波器组成,其中信号发生器的内阻是精确的50Ω。信号发生器可以产生上升时间在100ps以内的快速阶跃信号。

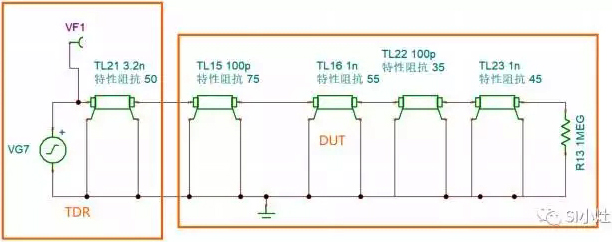

下图是使用TINA搭建的模型,其中左侧是TDR和一段约50cm长的线缆,右侧是一段阻抗不连续的一段传输线,信号源的上升时间为100ps,幅值为1V。

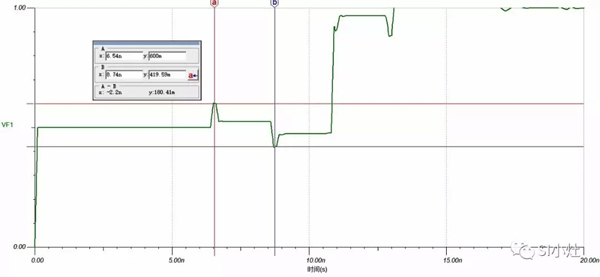

在VF1处测量到的电压信号如下图所示,由于DUT存在阻抗不连续,所以能够测量到变化的反射电压,DUT的末端是开路的,在末端的反射系数为1,所以被测件末端的电压会迅速提升到原来的两倍。

下图的a点对应的是DUT第一个阻抗为75Ω的位置,瞬时阻抗增大,反射系数ρ取正值,所以测量到的电压会增大,a点对应的时间约为6.4ns,是前面那段导线电延时的两倍;同理,b点对应的是上图中瞬时阻抗为35Ω的位置,在这个位置反射系数ρ为负值,所以对应位置电压减小,a点和b点之间的时间差为2.2ns,正好是这两点间电延时的两倍。

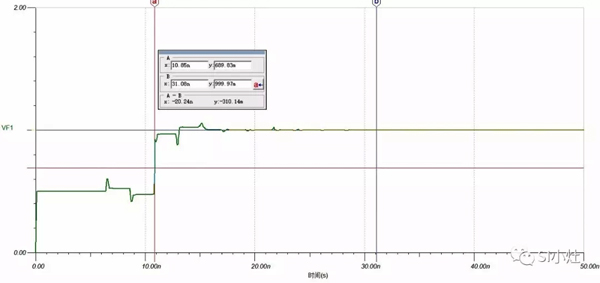

将时基扩大到10ns/div,能够看到信号在DUT末端的多次反射,但是由于末端是开路的,所以在达到稳态时的电压VF1(∞)=VG7(∞)=1V。

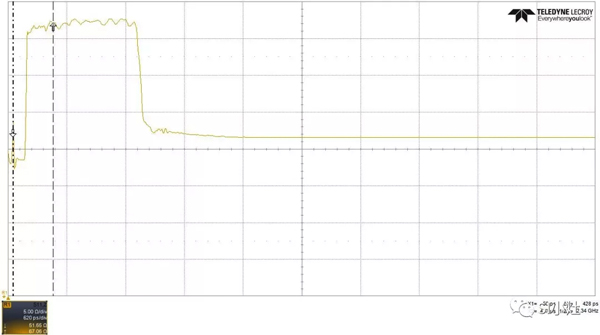

在实际测量中,TDR显示的纵轴不再是电压值,可以直接转换成阻抗,所以我们可以直接在TDR上查看阻抗的大小,下图是LeCroy公司SPARQ工具测量到的阻抗。

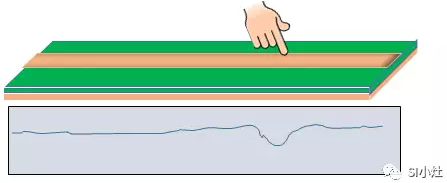

在使用TDR对微带传输线进行测量的时候,大家可以尝试一下用手轻触PCB走线,可以看到如下图所示的阻抗变化,TDR测量的阻抗曲线在某个位置阻抗突然减小,这是因为人的身体是导体,当手指接触到表层的PCB走线的时候,接触位置的等效并联了一个电容,使得容性增加,阻抗降低。

我们也可以利用这个方法去寻找微带传输线上阻抗不连续点在PCB的位置,用我们的人体去辅助定位。

TDR可以很好的测量无缘链路的互联设计,但是有时候TDR的测试结果也未必是“真实”的,告诉示波器测量到的结果有时候会更可靠,下面给大家举一个实例,这个也是我工作的时候遇到的第一个信号完整新方面的问题。

6、实例分析

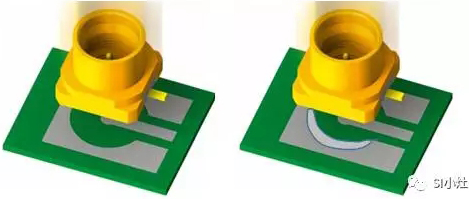

参加工作后测试的第一个项目是某3Gbps SerDes项目,EVB上采用的是SMP接口。可能是Layout的同事用错SMP接口的PCB封装了,SMP接口中多出了一圈额外的覆铜,参考下图右侧。多余的覆铜导致SMP接口处的电容变大,瞬时阻抗降低。

经过实测,SMP接口处的单端阻抗下降到了约30Ω,和50Ω的设计值相比,达到了40%偏差。我们当时还在想着信号质量一定会受到比较严重的影响,甚至有可能导致眼图闭合、产生大量误码。结果实际上,眼图和抖动并没有产生明显的恶化。

这是为什么呢?

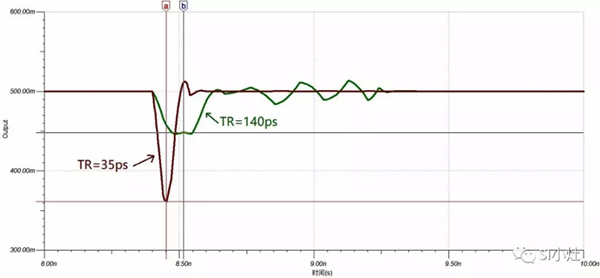

我们当时用来测试的TDR设备,上升时间是固定的35ps,而且不可调节。而35ps是一个非常快速地上升沿,10Gbps以上的信号在近端才会有这么快的上升沿,我们测试的信号速率是3.125Gbps,而且到SMP接口时已经经过了一段走线,所以实际信号的上升时间远大于35ps,我们使用TDR测量到的阻抗对于我们的被测信号来说是一个过于严苛的结果。

下图是使用TINA仿真出来的结果,当我们设置阶跃信号的上升时间为35ps的时候,反射更加严重,对应测量的瞬时阻抗也就越低,当阶跃信号上升沿为140ps的时候,明显有所改善。

从这个例子,我们可以看出来,如果测试条件不正确的话,有些测试得到的“真实数据”反而是不可靠的。在对高速信号进行分析的时候,一方面,我们需要从信号的角度去观察问题;另一方面,我们需要从多个角度进行测量和分析,这样才能够得到更可靠的结果。

对于高速系统,阻抗测量结果配合高速示波器测量到的结果往往会更加真实可靠。

7、Reference

Eric. Bogatin 《信号完整性分析》

Howard. Johnson 《高速数字设计》

本文使用的仿真工具是TINA,TINA是德州仪器(TI)公司提供的一款模拟电路仿真软件,可以在TI官网上免费下载。

粤公网安备 44030902003195号

粤公网安备 44030902003195号