东南大学 阳析 金石, 南京邮电大学 吕文俊,

美国国家仪器(NI) 田砾 潘晶

本文刊登于《微波射频技术》杂志 2015无线射频专刊

引言

随着物联网的兴起和移动互联网业务种类的日渐丰富,人们对蜂窝移动通信数据传输速率以及服务质量提出了更高的要求。由于能够充分挖掘空间维的自由度,在提高频谱效率的同时获得较好的功率利用率,大规模MIMO系统引起了国内外的广泛关注,并成为第五代(5G)无线通信系统最有潜力的无线传输技术之一。

大规模MIMO系统由于在基站侧引入大规模天线阵列,在带来性能增益的同时也带来了前所未有的挑战:1)灵活的软件无线电,可用于接收和发送射频信号;2)射频设备之间精确的时间和频率同步;3)具有高数据吞吐量的总线,用以传输和汇集海量的数据;4)高性能的处理能力,用以满足物理层和介质访问控制(MAC)执行时所需的实时性能需求。

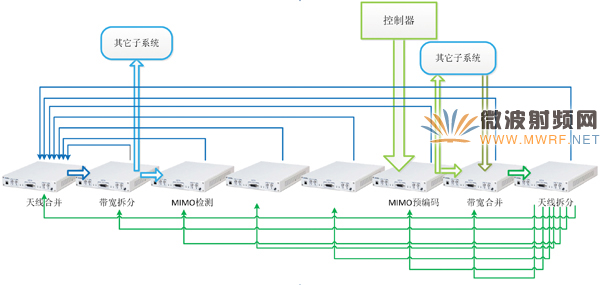

东南大学的金石教授团队,南京邮电大学朱洪波教授团队与NI一起合作,使用NI大规模MIMO的应用程序框架,采用一流的LabVIEW图形化系统设计软件和顶尖的NI USRPTM RIO软件无线电硬件,成功开发出了中国第一套16*2 Mini Massive MIMO原型验证系统,并进而实现了64*2的Massive MIMO原型验证系统进行高清(HD)视频流的流畅传输(见图1及图2)。

图1、东南大学—基于USRPTM RIO的大规模MIMO原型验证系统

图2、东南大学—基于USRPTM RIO的大规模MIMO原型验证系统配置面板

1、NI大规模MIMO应用程序框架

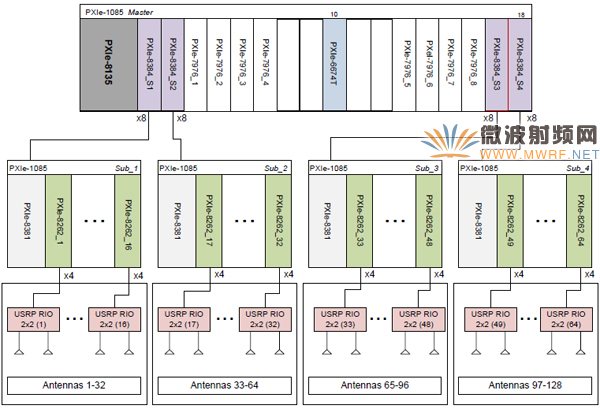

NI大规模MIMO应用程序框架,包含了搭建世界上最通用的、灵活的、可扩展的大规模MIMO原型验证系统所需的硬件和软件,该测试台支持实时处理以及在研发团队所感兴趣的频段和带宽上进行双向通信,使用NI软件无线电和LabVIEW系统设计平台软件。这种MIMO系统的模块化特性促使系统从仅有几个节点发展到128天线的大规模MIMO系统。并且随着无线研究的演进,基于硬件的灵活性,它也可以被重新部署到其他配置的应用中,比如点对点网络中的分布试节点,或多小区蜂窝网络等。图3给出了一个最多可支持128根天线的大规模MIMO原型验证系统的示意框图。

图3、基于PXI和USRPTM RIO的可扩展大规模MIMO系统框图[1]

从图中可以看出,整个系统的框架由PXIe-1085机箱搭建而成,采用层次化设计,数据由USRP-RIO采集后经PXIe-8262接口汇聚到各个子PXIe-1085机箱,每个子PXIe-1085机箱最多可连接16个USRP-RIO即构成32×32的MIMO,各个子PXIe-1085机箱再通过PXIe-8384和PXIe-8381汇聚到主PXIe-1085机箱,主PXIe-1085机箱上除配置PXIe-8135高性能嵌入式控制器外,还搭载了PXIe-7976的FPGA协处理器以用于提高数据的处理能力。

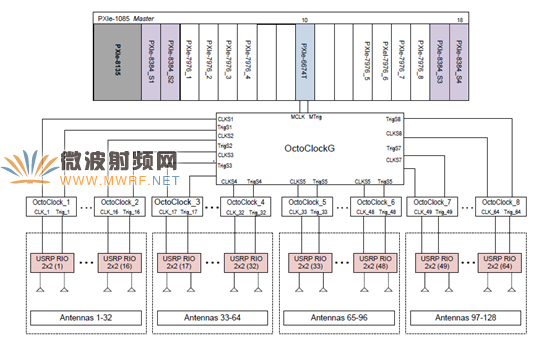

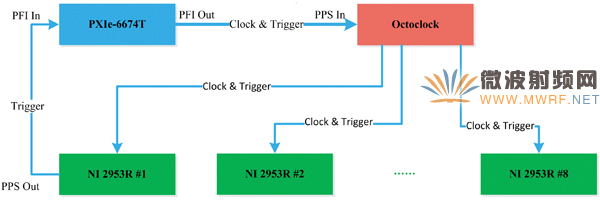

定时和同步对于任何一个需要部署大量无线电设备的系统来说都是至关重要的,对于大规模MIMO系统来说也是如此,图4展示了NI 基于PXI和USRP RIO的可扩展大规模MIMO系统的时钟连接框图。图中所用到的OctoClock模块为时钟模块,该模块既可使用内部集成的GPS锁定晶体振荡器(GPSDO)作为时钟源,也可采用外部的10MHz参考时钟和每秒脉冲数(PPS)信号作为时钟源和触发信号源。输入的时钟信号和触发信号可分别经由OctoClock模块放大和分发为8路信号,从而可同时提供给8个OctoClock模块或8台USRP设备在时钟和触发信号上的同步。

图4、系统时钟连接图[1]

基于NI平台的可扩展大规模MIMO系统的系统级同步原理可大致总结如下,PXIe-6674T定时和同步模块具有一个恒温晶体振荡器(OCXO),位于主机箱的第10槽,可生成一个非常稳定且精确的10MHz参考时钟(50 ppb的精确度)和提供一个数字触发信号给OctoClock-G时钟分配模块以用于时钟和触发信号的分发。之后,OctoClock-G放大并分发这一10MHz参考时钟信号(MCLK)和触发信号(MTrig)至8个OctoClock模块,接着每个OctoClock模块再以一对八的比例提供给USRP RIO设备,从而确保64个USRP RIO设备的所有天线共享10MHz的参考时钟和主触发信号。这样通过PXIe-6674T定时和同步模块和OctoClock时钟分配模块整个系统中的所有PXI机箱和无线电设备都共享一个通用10MHz参考时钟和一个数字触发信号,从而确保了整个系统的系统级同步,各个无线电设备可同步进行数据采集和生成。

2、Mini Massive MIMO原型验证系统实例

东南大学的金石教授团队、南京邮电大学朱洪波教授团队与NI一起合作,快速并成功搭建完成了16*2 Mini Massive MIMO原型验证系统。本节将从三个方面进行详细介绍,包括系统的整体架构、系统时钟和触发信号的产生及分配、上下行链路的数据处理流程。

A、系统的整体架构

1)、硬件部分

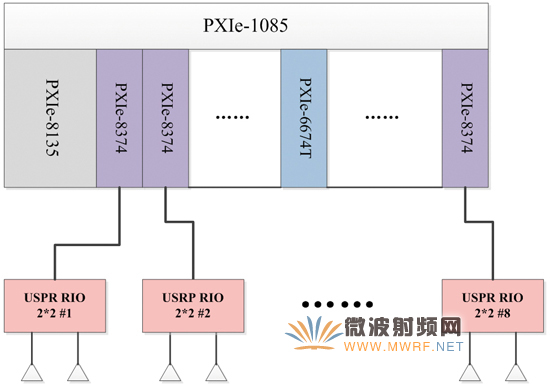

Mini Massive MIMO原型验证平台的系统框图如图5所示。

图5、Mini Massive MIMO原型验证系统框图

系统主要由NI PXI机箱和软件无线电节点USRPTM RIO组成。其中,USRPTM RIO实际使用为NI 2953R,其内部包含一个可编程(Xilinx Kintex-7)FPGA和两个40MHz 带宽的RF收发器,中心频点可配置在1.2-6GHz的频段范围内,最大的信号发射功率为15dBm,表1给出了NI 2953R的详细硬件参数。

表1、NI 2953R的详细硬件参数

| 系统参数 | 值 |

| 中心频率 | 1.2 – 6.0 GHz |

| RF带宽 | 40 MHz |

| 每个设备的RF通道数 | 2 |

| ADC采样率 | 120 MS/s |

| ADC分辨率 | 14 bit |

| DAC采样率 | 400 MS/s |

| DAC分辨率 | 16 bit |

| 板载FPGA | Xilinx Kintex-7 XC7K410T |

| 数字后端接口 | PCI-Express Gen 1 x4 |

图中,高性能嵌入式控制器PXIe-8135插于PXIe-1085机箱的第1个插槽,定时和多机箱同步模块PXIe-6674T插于第10槽,8个NI 2953R分别通过PXIe-8374或PXIe-8262接口板卡连接到PXIe-1085机箱的其它8个插槽,从而每个NI 2953R能够以最大800MB/s的速率将数据汇集到PXI机箱并通过机箱背板进行板间数据交换以实现软件无线电节点间、软件无线电节点与PXIe-8135控制器间的数据传递。

由于所搭建的Mini Massive MIMO原型验证系统是TDD系统,且采用简化的LTE无线帧格式和使用OFDM无线传输技术,考虑到系统的可扩展性和系统未来带宽的增加(如引入载波聚合等先进技术),同时为满足系统速率要求和有限资源限制,Mini Massive MIMO在设计时考虑将整个系统划分为多个子系统(并保留相关数据接口),每个子系统由8个NI 2953R和其对应的1个PXIe-1085机箱组成,负责处理分配给当前子系统的固定带宽的数据,因而图3所示的Mini Massive MIMO系统框图实际仅为一个子系统的系统框图,需要注意的是,除了所处理的数据所在频带不同外,各个子系统的结构与各部分功能均完全一致。

此文主要针对当前子系统(即16*2 Mini Massive MIMO系统)进行介绍。根据实现功能的不同,16*2的Mini Massive MIMO系统中的8个NI 2953R被划分为不同的功能模块,如图4所示,它们分别是天线合并模块、带宽拆分模块、信道估计模块、MIMO检测模块、射频通道校准模块、MIMO预编码模块、带宽合并模块和天线拆分模块。其中,天线合并模块和天线拆分模块分别负责汇聚来自各个天线的数据和将数据分发至各个物理天线,带宽拆分模块负责将该子系统中整带宽的数据划分成不同子带并分配至其它子系统,带宽合并模块负责汇聚其它子系统传输过来的子带的数据,MIMO检测模块和MIMO预编码模块则是分别负责对该子系统所负责的子带数据进行检测译码和预编码。

图6、系统功能模块划分

对于上行链路,接收到的数据首先会汇聚到天线合并模块,然后由天线合并模块传递给带宽拆分模块进行数据的按带宽划分以分配给不同的子系统,各子系统的信道估计模块接收到来自带宽拆分模块的数据后进行信道估计,并将估计出的信道信息传递给MIMO检测模块以用于用户数据的检测;同样的对于下行链路,要发送的数据首先由控制器传送给MIMO预编码模块,MIMO预编码模块根据信道估计模块和射频通道校准模块的信息对数据进行预编码后将已预编码的数据传递给带宽合并模块,以合并其它子系统所处理的带宽的数据从而形成整带宽数据,最后整带宽的数据将会被传送给天线拆分模块以实现所要发送的数据被分配至各个实际的物理天线进行发送。

2)、软件部分

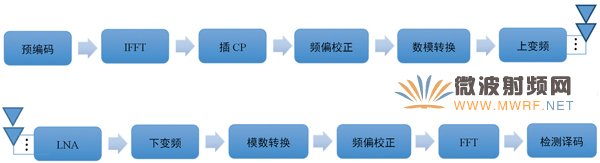

系统的软件部分包括FPGA程序与上位机程序,其中,FPGA程序运行于NI 2953R上,主要完成接收信号或发射信号的下、上变频,模数、数模转换以及硬件部分所述的模块功能,信号处理流程见图8。

上位机程序主要负责设置系统的相关参数、配置各NI 2953R、产生所需发送数据或显示系统接收到的数据以及启动或停止系统的运行。其中系统相关参数包括:系统的载波频率,发送功率,采样率,调制方式等等,如当前系统的载波频率为4.1GHz,采样率为15.36MS/s,调制方式为16QAM。

B、系统时钟和触发信号的产生和分配

参考于NI 基于PXI和USRP RIO的可扩展大规模MIMO系统的时钟连接,Mini Massive MIMO系统的时钟和触发信号分发网络如图7所示。

图7、Mini Massive MIMO系统的时钟和触发信号分发网络

系统采用OctoClock模块构建时钟和触发信号分发网络,系统的触发信号和源时钟信号从PXIe 6674T引出后输入到OctoClock模块进行路由和分发,而后OctoClock模块输出端的8路时钟信号和8路触发信号分别通过等长的传输电缆输入到8个NI 2953R以确保系统各个NI 2953R的时钟与触发信号的同步。源触发信号的产生是通过设定主NI 2953R然后在主NI 2953R中以软件触发的方式发出一个启动脉冲来实现。该启动脉冲信号(源触发信号)在主设备的一个输出端口上被引出,并输入至PXIe-6674T中放大,然后传递到OctoClock模块,并沿着电缆向下分布到系统中的各个NI 2953R设备(包括主设备自己),它的主要作用为设置参考时钟边沿以用于各个NI 2953R发射和接收时同步启动采集。

初步测试结果显示在此同步架构下,参考时钟偏移在100 ps以内,触发偏移在1.5 ns以内。

C、上下行链路的数据处理流程

对于上行链路,系统中的8个NI 2953R的16根天线采集到的射频信号经过射频通道的低噪声放大、下变频和ADC采样量化后被分别送入到各个NI 2953R的FPGA中进行下采样、频率偏移校正、IQ信号校正和FFT,之后压入P2P FIFO或本地FIFO中以用于传递到相应模块进行后续处理,如信道估计,信号检测等。

图8、上下行链路的数据处理流程

对于下行链路,数据首先由控制器传递到MIMO预编码模块进行预编码,然后通过带宽合并和天线拆分模块分发到8个NI 2953R,在各个NI 2953R的FPGA中进行OFDM调制、频率偏移校正和IQ信号校正,校正过后的数据再被送入到各个射频通道进行数模转换和上变频最后通过天线发送出去。

3、系统的实测结果

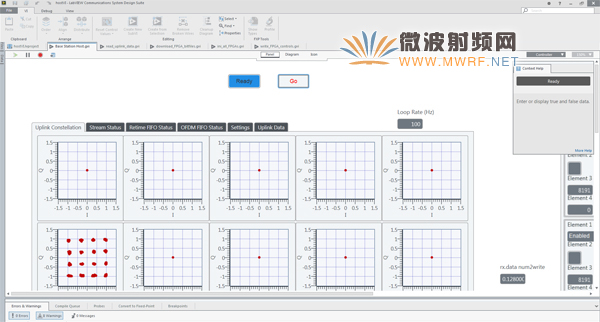

系统的实测结果如图9所示。图中展示了在LabVIEW Communication下的程序前面板框图,从图中可以看出,当前有一个用户在发送上行数据,数据调制方式为16QAM,由于没有其它用户干扰,星座图的星座点较细系统性能较好。

图9、LabVIEW Communication下系统实测结果

4、结论

NI技术通过LabVIEW系统设计软件以及USRPTM RIO和PXI平台的组合正在彻底革新高端科研系统的原型设计方法。文中结合具体实例介绍了一种搭建大规模多入多出(MIMO)系统的可行方法来进一步推进5G的研究。该应用程序框架中使用的各种NI技术的独特组合实现了大量无线电设备在时间和频率上的同步,而且PCI Express技术也提供了以15.7GB/s速率上下行传输和汇集I-Q信号所需的吞吐量。层次化的设计,各部分功能模块相对独立,具有较强的可扩展性。FPGA的数据流设计方式简化了物理层和介质访问控制层上的高性能处理,系统的核心算法如OFDM调制解调、信道估计与MIMO检测等均在高性能的FPGA端完成,满足实时处理的要求。

为保证这些产品能满足无线技术研究人员的特定需求,NI正在积极地与行业领先的研发人员和国内外世界名校进行合作。这些合作推动了一些研究领域取得令人兴奋的进展,同时也促进了需要和正在使用大规模MIMO应用程序框架等工具的工程师和科研人员之间的方法、IP和最佳实践共享。

参考文献

[1]. L. Erik, “5G Massive MIMO Testbed: From Theory to Reality”, Oct 01, 2014. http://www.ni.com/white-paper/52382/en/

[2]. J. Vieira, S. Malkowsky, K. Nieman, et al. “A flexible 100-antenna testbed for Massive MIMO”, (2014) IEEE Globecom 2014 Workshop - Massive MIMO: From Theory to Practice. http://lup.lub.lu.se/record/4857731

本文刊登于微波射频网旗下《微波射频技术》杂志 2015无线射频专刊,未经允许谢绝转载。

粤公网安备 44030902003195号

粤公网安备 44030902003195号