NIзҹўйҮҸдҝЎеҸ·ж”¶еҸ‘еҷЁзҡ„FPGAзј–зЁӢ

дёӨдёӘйЎ№зӣ®ж ·дҫӢFPGA VIд№Ӣй—ҙзҡ„дё»иҰҒеҢәеҲ«жҳҜпјҡVST StreamingйЎ№зӣ®ж ·дҫӢдҪҝз”ЁиҪ»иҙЁжңәеҲ¶е®ҢжҲҗдёҺдё»жңәд№Ӣй—ҙзҡ„ж•°жҚ®ж”¶еҸ‘гҖӮе®ғйҮҮз”Ёз®ҖеҚ•зҡ„жөҒжҺ§еҲ¶еҷЁпјҢж”ҜжҢҒеҹәжң¬и§ҰеҸ‘гҖҒиҝһз»ӯе’Ңй—ҙж–ӯжөҒпјҢд»ҘеҸҠжәўеҮәе’ҢдёӢжәўжЈҖжөӢгҖӮиҝҷдәӣжҺ§еҲ¶еҷЁдёӯж–ӯдҝЎеҸ·жәҗдёҺзӣ®зҡ„ең°д№Ӣй—ҙзҡ„2зәҝжҸЎжүӢдҝЎеҸ·пјҢжңүж•Ҳең°йҖүйҖҡж•°жҚ®жөҒгҖӮжҺ§еҲ¶еҷЁдёҚж”ҜжҢҒе…Ё4зәҝжҸЎжүӢж–№жЎҲпјҢиҜҘж–№жЎҲиғҪеӨҹи°ғж•ҙдёҠжёёиҠӮзӮ№жҲ–иҖ…иў«дёӢжёёиҠӮзӮ№жүҖи°ғж•ҙпјӣеӣ жӯӨпјҢзі»з»ҹзү№жҖ§еҢ–д»ҘеҸҠзЎ®дҝқиҝҷдәӣжөҒжҺ§еҲ¶еҷЁжҺ§еҲ¶зҡ„жүҖжңүFIFOеқҮиғҪеӨҹд»ҘиҰҒжұӮзҡ„йҖҹзҺҮдә§з”ҹжҲ–ж¶ҲиҖ—ж•°жҚ®е°ұиҗҪеҲ°дәҶзЁӢеәҸе‘ҳзҡ„иӮ©дёҠгҖӮеңЁVST StreamingйЎ№зӣ®ж ·дҫӢдёӯйҖҡиҝҮз®ҖеҚ•зҡ„жӣҙж”№й»ҳи®Өжғ…еҶөдёӢе®ҢжҲҗдёҺдё»жңәд№Ӣй—ҙзҡ„ж•°жҚ®ж”¶еҸ‘зҡ„FIFOпјҢеҸҜд»Ҙж”ҜжҢҒж•°жҚ®жөҒдј иҫ“еҲ°VST FPGAдёҠзҡ„е…¶д»–дҪҚзҪ®д»ҘиҝӣиЎҢиҝӣдёҖжӯҘеӨ„зҗҶпјҢжҲ–иҖ…йҖҡиҝҮPXI ExpressиғҢжқҝпјҢеҲ©з”ЁP2Pдј иҫ“иҮіе…¶д»–жЁЎеқ—гҖӮ

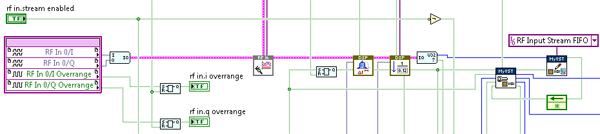

еӣҫ14.FPGAжөҒжҺ§еҲ¶еҷЁе’ҢFIFOе°ҒиЈ…е®һзҺ°еҹәжң¬жөҒжҺ§еҲ¶пјҢ并且иғҪеӨҹиҪ»жқҫж”№еҸҳж•°жҚ®жөҒзҡ„жәҗеҸҠзӣ®зҡ„ең°и·ҜзәҝгҖӮ

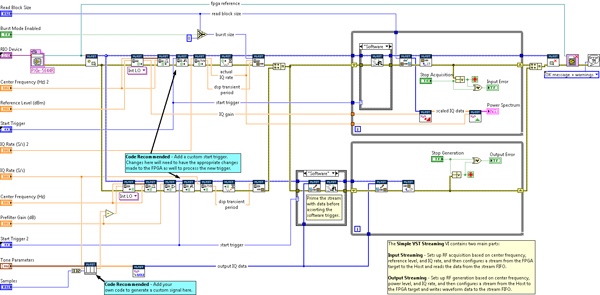

зҺ°еңЁжқҘзңӢVST StreamingйЎ№зӣ®ж ·дҫӢзҡ„дё»жңәз«ҜпјҢиҷҪ然жңәеҲ¶дёҺSimple VSA/VSGдёҚеҗҢ,д№ҹеӯҳеңЁзұ»дјјдәҺд»ӘеҷЁи®ҫи®Ўеә“дё»жңә组件зҡ„йӣҶжҲҗпјҢгҖӮVST StreamingйЎ№зӣ®ж ·дҫӢдёҚдҪҝз”ЁLabVIEWзұ»пјҢиҖҢжҳҜе°ҶеҠҹиғҪз®ҖеҚ•ең°йӣҶжҲҗеҲ°еӯҗVIдёӯпјҢ并е°ҶдјҡиҜқдј йҖ’иҮіеӯҗVIд№Ӣй—ҙзҡ„еҜ„еӯҳеҷЁжҖ»зәҝгҖӮжӯӨеҜ„еӯҳеҷЁжҖ»зәҝдјҡиҜқиҝҳеҢ…еҗ«жңүFPGA VI еј•з”ЁпјҢеӣ жӯӨжүҖжңүиҝҷдәӣеӯҗVIдёҚд»…иғҪеӨҹи®ҝй—®еҜ„еӯҳеҷЁжҖ»зәҝйҖҡдҝЎзӯ–з•ҘпјҢиҖҢдё”иҝҳеҸҜд»Ҙи®ҝй—®NI-RIO FIFOе’ҢжҺ§еҲ¶еҷЁгҖӮеҸҰеӨ–пјҢдёҚеӯҳеңЁзӢ¬з«Ӣзҡ„ж•°жҚ®йҮҮйӣҶе’Ңз”ҹжҲҗдјҡиҜқпјӣжүҖжңүVIеқҮдҪҝз”ЁеҗҢдёҖдјҡиҜқгҖӮ

еӣҫ15.VST StreamingйЎ№зӣ®ж ·дҫӢдё»жңәжҺҘеҸЈе…·жңүдёҖдёӘеҹәдәҺеҜ„еӯҳеҷЁжҖ»зәҝзҡ„дјҡиҜқзәҝпјҢз”ЁдәҺйҮҮйӣҶе’Ңз”ҹжҲҗsubVIгҖӮеңЁйҖ»иҫ‘дёҠпјҢжӯӨж ·дҫӢе°ҶйҮҮйӣҶе’Ңз”ҹжҲҗеҲҶз»„жҲҗдёәзӢ¬з«Ӣзҡ„иЎҢпјҢд»Ҙж–№дҫҝйҳ…иҜ»гҖӮ

VST StreamingйЎ№зӣ®ж ·дҫӢжҸҗдҫӣдёӨдёӘдё»жңәж ·дҫӢгҖӮиҫғз®ҖеҚ•зҡ„дёҖдёӘж ·дҫӢжҠҠд»ҺVSTеӨ„йҮҮйӣҶеҫ—еҲ°зҡ„еўһеӨҡзҡ„жҲ–иҖ…иҝһз»ӯзҡ„жіўеҪўж•°жҚ®дј иҫ“иҮіVSTиҝӣиЎҢз”ҹжҲҗпјҢгҖӮжҜ”иҫғй«ҳзә§зҡ„ж ·дҫӢиҜҙжҳҺдәҶеӨҡдёӘVSTзҡ„MIMOеҗҢжӯҘгҖӮ

еӣҫ16.иҝҷдәӣж ·дҫӢиҜҙжҳҺдәҶVST StreamingйЎ№зӣ®ж ·дҫӢзҡ„дё»жңәжҺҘеҸЈ

4. д»ӘеҷЁй©ұеҠЁFPGAжү©еұ•

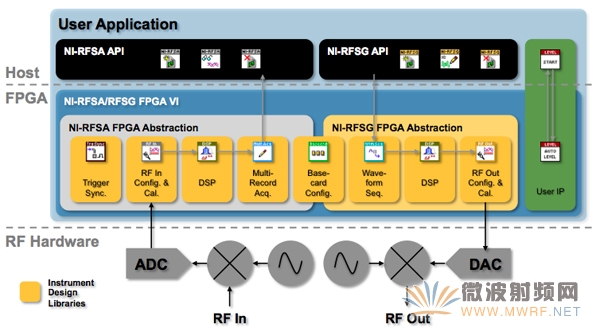

д»ӘеҷЁй©ұеҠЁFPGAжү©еұ•жҸҗдҫӣдәҶдёҖз§Қе…је®№NI-RFSAе’ҢNI-RFSGд»ӘеҷЁй©ұеҠЁзҡ„VST FPGAзј–зЁӢж–№жі•гҖӮFPGAдёҠзҡ„жҠҪеҸ–еұӮе®һзҺ°дәҶжүҖйңҖиҰҒзҡ„д»ӘеҷЁй©ұеҠЁеҠҹиғҪпјҢеҗҢж—¶жҸҗдҫӣжҺҘеҸЈд»Ҙж”№е–„е…·дҪ“еә”з”Ёзҡ„FPGAгҖӮиҷҪ然дёҚеғҸд»ӘеҷЁи®ҫи®Ўеә“зҡ„зӣҙжҺҘзј–зЁӢйӮЈж ·зҒөжҙ»пјҢ然иҖҢд»ӘеҷЁй©ұеҠЁFPGAжү©еұ•ж”ҜжҢҒзҡ„дҝ®ж”№зұ»еһӢдёҺж ҮеҮҶдҝЎеҸ·еҲҶжһҗд»Әе’ҢдҝЎеҸ·еҸ‘з”ҹеҷЁзҡ„еҹәдәҺи®°еҪ•зҡ„йҮҮйӣҶе’Ңз”ҹжҲҗжЁЎејҸзӣёдёҖиҮҙгҖӮ

еӣҫ17. д»ӘеҷЁй©ұеҠЁFPGAжү©еұ•жһ¶жһ„еҢ…еҗ«VSTд»ӘеҷЁи®ҫи®Ўеә“пјҢ并且еўһеҠ дәҶдёҖдёӘжҠҪеҸ–еұӮд»ҘдҝқжҠӨ组件гҖӮз”ЁжҲ·IPдёҚеңЁжӯӨд»Јз ҒдёӯпјҢз”ұдё»жңәиҝӣиЎҢжҺ§еҲ¶пјҢ并且дёҚеҸ—йў„зј–иҜ‘е°Ғй—ӯжәҗNI-RFSAе’ҢNI-RFSGзҡ„еҪұе“Қ

5. еӨ§еһӢFPGAејҖеҸ‘иҖғиҷ‘дәӢйЎ№

The Virtex-6 LX195T FPGA on the NI PXIe-5644R and the NI PXIe-5645R is a large FPGA, though the full suite of instrument design libraries consumes a considerable fraction of the available resources. As such, compilation times can take 5 hours or more when using the NI LabVIEW FPGA Compile Cloud Service, depending on the complexity and resource utilization of the FPGA design. Furthermore, FPGA compilation is a non-deterministic process, and as a design consumes more FPGA resources, the repeatable compilation success rate drops below 100%. For such designs, initiating multiple compiles in parallel can help to ensure a successful compilation in approximately the same time as a single compilation. Table 3. provides some estimates for the different FPGA designs discussed in this paper.

| FPGAи®ҫи®Ў | иҝ‘дјјзј–иҜ‘ж—¶й—ҙ | иҝ‘дјјзј–иҜ‘жҲҗеҠҹзҺҮ | LUTеҚ з”ЁзҺҮ | и§ҰеҸ‘еҷЁеҚ з”ЁзҺҮ | DSPзүҮеҚ з”ЁзҺҮ | еқ—RAMеҚ з”ЁзҺҮ |

| VST StreamingйЎ№зӣ®иҢғдҫӢ | 4 е°Ҹж—¶ | 90% | 27% | 30% | 31% | 20% |

| Simple VSA/VSGйЎ№зӣ®иҢғдҫӢ | 5 е°Ҹж—¶ | 80% | 50% | 49% | 31% | 39% |

| д»ӘеҷЁй©ұеҠЁFPGAжү©еұ• | 6 е°Ҹж—¶ | 75% | 67% | 62% | 31% | 45% |

иЎЁ3. еҗ„з§ҚVST FPGAи®ҫи®Ўзҡ„зј–иҜ‘ж—¶й—ҙгҖҒжҲҗеҠҹзҺҮе’ҢFPGAеҚ з”ЁзҺҮгҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·