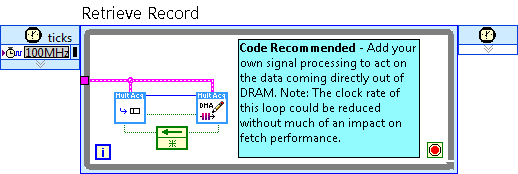

图9.读取循环提供了在已采集数据返回主机之前对其进行处理的机会。在默认情况下,读取回路返回原始数据。

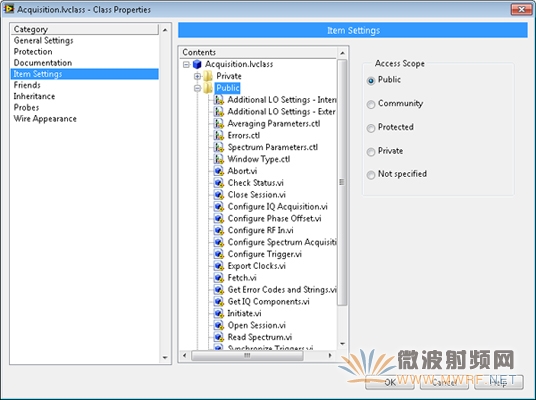

虽然顶层FPGA VI集合了13个仪器设计库的功能,然而在主机上对所有这些库进行独立编程仍然不方便,并且此应用层主机代码一点也不像传统的VSA或者VSG API。为了解决此问题,Simple VSA/VSG项目样例包含了一个附加主机层,将这些仪器设计库集合在一个接口内,提供了与供应商定义的VSA/VSG API相类似的功能。LabVIEW类为此提供了一个方便的机制,即提供一个严格类型的会话,公有和私有方法,以及一个方便的子VI图标头文件保持机制。请注意,LabVIEW类中面向对象的继承,并没有用于此主机接口。

图10.LabVIEW类提供了一个方便的功能集合和主机接口保持机制。

这个简单的VSA/VSG样例项目还提供了常见的RF VSA和VSG操作所用的若干个主机样例,这些样例说明了如何正确使用主机接口。这些样例涵盖频域和I/Q采集;CW和基于序列的波形发生;以及多输入多输出(MIMO)同步。

图11.一些主机样例说明了Simple VSA/VSG项目样例使用基于类的主机接口的方法

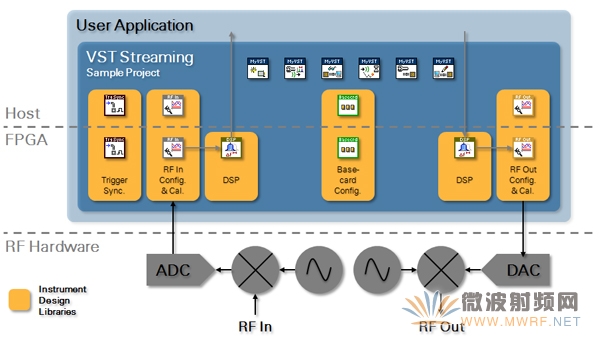

简单VSA/VSG项目样例包含极多功能,并提供了熟悉的主机接口。然而该实用工具的代价就是代码的复杂度。具体地说,FPGA上的DRAM采用基于波形的抽取,显著增加代码量、复杂度,以及VST FPGA资源占用。然而,并不是所有应用均需要基于波形或者仪器数据移动范式。一些应用更加适合实时流数据移动架构。对于这些应用,VST Streaming项目范例是一个更好的起点,自定义的自由度更广。

图12.VST Streaming项目样例在主机和FPGA上集合了仪器设计库,提供了一个灵活地开发实时、低滞后信号处理和嵌入式应用的起

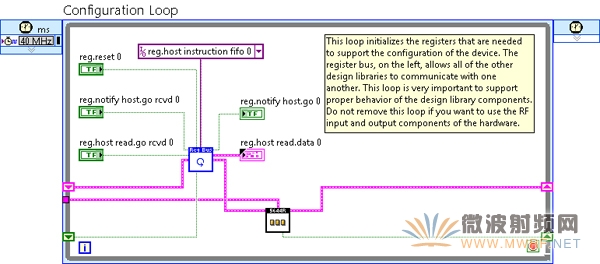

VST Streaming项目样例的顶层FPGA VI的架构与简单VSA/VSG项目样例相近。然而如果仔细考察,会发现要简单得多。可以明显看出,VST Streaming没有代码量极多的配置过程。配置循环也简单得多,只有一条寄存器总线而非两条,并且所有子系统均包在一个子VI中。

图13.VST Streaming项目样例中的FPGA VI配置回路,只有一个寄存器总线接口,比Simple VSA / VSG要简单得多

粤公网安备 44030902003195号

粤公网安备 44030902003195号