жүӢжңәеҠҹзҺҮж”ҫеӨ§еҷЁзҡ„еҠҹзҺҮеҢ…з»ңи·ҹиёӘ

жӮЁжҳҜеҗҰеҗ¬еҲ°жңүдәәжҠұжҖЁжҜҸеӨ©иҰҒдёә4Gз”өиҜқе……з”өдёӨж¬ЎпјҹеҫҲйҒ—жҶҫпјҢд»–еҜ№иҮӘе·ұзҡ„жүӢжңә并дёҚеӨӘж»Ўж„ҸгҖӮ

йҡҸзқҖдәә们еҜ№й«ҳйҖҹж•°жҚ®иҜ»еҶҷзҡ„йңҖжұӮдёҺж—ҘдҝұеўһпјҢиҖҢз”өжұ зҡ„е®№йҮҸеҚҙж— жі•и·ҹдёҠйҖҡдҝЎжҠҖжңҜеүҚиҝӣзҡ„жӯҘдјҗпјҢиҝҷз§ҚзҺ°иұЎдёҖзӣҙеұЎи§ҒдёҚйІңгҖӮиҝҷ并дёҚжҳҜз”өжұ зҡ„й—®йўҳпјҢиҖҢжҳҜжҲ‘们йңҖиҰҒдёҖз§ҚжҠҖжңҜжқҘдҪҝжүӢжңәж”ҫеӨ§еҷЁеҸҳеҫ—жӣҙдёәејәеӨ§гҖӮиҝҮеҺ»жҷ®йҒҚйҮҮз”Ёжҷ®йҖҡзҡ„DC-DCиҪ¬жҚўеҷЁжқҘжҺ§еҲ¶жүӢжңәз”өжұ з”өйҮҸжөҒе…ҘдёҚеҗҢзҡ„иҠҜзүҮгҖӮиҝҷеҢ…жӢ¬е°ҶжүӢжңәдҝЎеҸ·й©ұеҠЁеӣһеҹәз«ҷзҡ„еҠҹзҺҮж”ҫеӨ§еҷЁ(PA)пјҢеҜ№дәҺ2Gе’Ң3GдҝЎеҸ·пјҢз”ұдәҺеі°еқҮеҠҹзҺҮжҜ”(PAPR)зӣёеҜ№иҫғе°ҸпјҢиҜҘеҠҹзҺҮж”ҫеӨ§еҷЁеҸҜд»ҘеҫҲеҘҪең°е·ҘдҪңгҖӮдҪҶйҡҸзқҖжҠҖжңҜд»ҺGSMеҸ‘еұ•еҲ°GPRSгҖҒWCDMAзӣҙиҮіHSPAпјҢPAPRд№ҹеӨ§е№…еҚҮй«ҳгҖӮзҺ°еңЁLTEжҲ–4Gе…·жңүйқһеёёй«ҳзҡ„PAPRпјҢжһҒеӨ§еҪұе“ҚдәҶжүӢжңәзҡ„иҖ—з”өйҮҸгҖӮеӣҫ1жҳҫзӨәзҡ„жҳҜеҹәдәҺи®ҫеӨҮз”өжұ зү№е®ҡеҠҹзҺҮиҫ“е…Ҙзҡ„е…ёеһӢPAиҫ“еҮәйҡҸжҠҖжңҜеҸ‘еұ•зҡ„еҸҳеҢ–гҖӮ

еӣҫ1.дёҚеҗҢж— зәҝж ҮеҮҶзҡ„PAPRжј”зӨәпјҡиҜҘеӣҫжҳҫзӨәзҡ„жҳҜдёҖдёӘе…ёеһӢPAзҡ„з”өжұ иҫ“е…ҘеҠҹзҺҮ(Pin)е’Ңиҫ“еҮәеҠҹзҺҮд№ӢжҜ”гҖӮдҝЎеҸ·еҠҹзҺҮеҺӢзј©йҡҸзқҖдёҚеҗҢзҡ„PAи®ҫи®ЎиҖҢејӮпјҢдҪҶPAPRеҲҷдҝқжҢҒдёҚеҸҳгҖӮ

DC-DCиҪ¬жҚўеҷЁеңЁдҝЎеҸ·еҠҹзҺҮиҫҫеҲ°еі°еҖјж—¶д»ҘзәҝжҖ§ж–№ејҸеҗёж”¶и®ҫеӨҮз”өжұ зҡ„з”өйҮҸпјҢиҝҷз§Қж•ҲзҺҮ并дёҚй«ҳгҖӮжҸҗй«ҳз”өиғҪж•ҲзҺҮзҡ„дёҖз§Қж–№ејҸжҳҜйў„жөӢжүӢжңәдҝЎеҸ·зҡ„еі°еҖјпјҢ然еҗҺд»…еҗ‘PAжҸҗдҫӣжүҖйңҖзҡ„з”өйҮҸгҖӮиҝҷз§Қдҫӣз”өж–№ејҸз§°дёәеҠҹзҺҮеҢ…з»ңи·ҹиёӘ(ET)гҖӮеӣҫ2жҳҫзӨәзҡ„жҳҜETж–№жі•гҖӮ

еӣҫ2. еҪ“дј иҫ“жіўеҪўпјҲд»ҘзәўиүІж ҮзӨәпјүзҡ„еҠҹзҺҮдёҚдёәеі°еҖјж—¶пјҢETдҫӣз”өж–№жі•пјҲд»Ҙи“қиүІж ҮзӨәпјүеҸҜеҮҸе°‘з”өиғҪзҡ„жөӘиҙ№гҖӮ

еңЁиҝҮеҺ»еҚҒе№ҙдёӯпјҢеҠҹзҺҮеҢ…з»ңи·ҹиёӘжҠҖжңҜе·Із»Ҹи§ЈеҶідәҶеҹәз«ҷзҡ„иҝҷдёҖйҡҫйўҳпјҢдёҚд»…иҠӮзңҒдәҶеҠҹиҖ—пјҢиҝҳеҸҜйҳІжӯўиҝҮзғӯпјҢиҝҷжҳҜз”ұдәҺPAеҸҜд»ҘеӨ„зҗҶеӨ§зәҰ200WжҲ–жӣҙй«ҳзҡ„еҠҹзҺҮгҖӮзҺ°еңЁпјҢеҚҠеҜјдҪ“жҠҖжңҜе·Із»ҸеҸ‘еұ•еҲ°дёҖе®ҡзЁӢеәҰпјҢDC-DCиҪ¬жҚўеҷЁеҸҜз”ЁдәҺ移еҠЁи®ҫеӨҮпјҢеҸҜдёәPAжҸҗдҫӣжүҖйңҖзҡ„и°ғеҲ¶еҠҹзҺҮпјҢиҝҷз§ҚжҠҖжңҜеҮәзҺ°еҫ—йқһеёёеҸҠж—¶пјҢеӣ дёәLTEзӯү4GжҠҖжңҜжӯЈеңЁдёҚж–ӯең°иҝ«дҪҝдәә们жҸҗй«ҳPAзҡ„ж•ҲзҺҮгҖӮзҺ°еңЁжҲ‘们еҰӮдҪ•жөӢиҜ•иҝҷдёҖж–°жҠҖжңҜпјҹд»ҘдёӢжҳҜдёҖдёӘPAжөӢиҜ•и§ЈеҶіж–№жЎҲзҡ„жөӢиҜ•жөҒзЁӢжҰӮиҝ°гҖӮ

ETжөӢиҜ•зҡ„жҢ‘жҲҳ

ETжөӢиҜ•дҪҝеҫ—еҺҹжң¬е°ұйқһеёёеӨҚжқӮзҡ„зі»з»ҹеҸҳеҫ—жӣҙдёәеӨҚжқӮгҖӮйҮҮз”ЁETжҠҖжңҜзҡ„第дёҖдёӘжҢ‘жҲҳе°ұжҳҜз”ҹжҲҗи°ғеҲ¶зҡ„дҫӣз”өз”өжәҗпјҢиҜҘз”өжәҗйңҖиҰҒй«ҳиҫҫ2Wзҡ„еҠҹзҺҮе’Ңж•°еҚҒе…Ҷиө«е…№зҡ„еёҰе®ҪгҖӮиҝҷдәӣиҰҒжұӮеҜ№дәҺз”өжәҗжқҘиҜҙ并дёҚеёёи§ҒпјҢеӣ жӯӨи®ёеӨҡPAеҲ¶йҖ е•ҶдҪҝз”Ёз»Ҹж”№иүҜзҡ„DC-DCиҪ¬жҚўеҷЁжқҘжү§иЎҢеҠҹзҺҮи°ғеҲ¶гҖӮиҝҷдәӣиҠҜзүҮеҸҜжҺҘеҸ—зӣҙжөҒз”өжәҗгҖҒз”ЁдәҺжҺ§еҲ¶ж”ҫеӨ§еҷЁеўһзӣҠзҡ„еҢ…з»ңжіўеҪўд»ҘеҸҠз”ЁдәҺжҺ§еҲ¶иҠҜзүҮзҡ„дёҖдәӣж•°еӯ—зәҝзҡ„иҫ“е…ҘгҖӮиҫ“еҮәжҳҜдёҖдёӘй«ҳеҠҹзҺҮи°ғеҲ¶жіўеҪўпјҢз”ЁдәҺжҸҗй«ҳеҫ…жөӢж”ҫеӨ§еҷЁзҡ„ж”ҫеӨ§еҠҹиғҪгҖӮиҜҰи§Ғеӣҫ3дәҶи§Је…ёеһӢзҡ„RF PAжөӢиҜ•и®ҫзҪ®пјҢиҜҘи®ҫзҪ®е·ІиҝӣиЎҢжү©еұ•пјҢеҸҜж”ҜжҢҒETгҖӮ

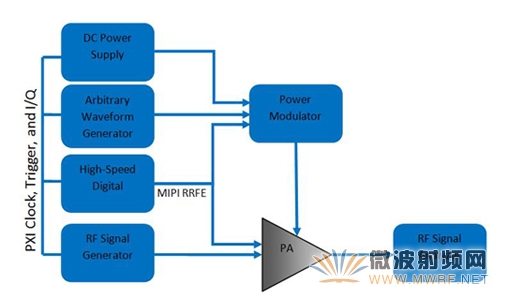

еӣҫ3. еӣҫдёәRF PAжөӢиҜ•зҡ„е…ёеһӢй…ҚзҪ®пјҢеҸҜе®һзҺ°еҢ…з»ңи·ҹиёӘгҖӮ

д»ҺжөӢиҜ•е’Ңзү№еҫҒи®°иҝ°зҡ„и§’еәҰжқҘзңӢпјҢдё»иҰҒзҡ„жҢ‘жҲҳеңЁдәҺеҜ№жү§иЎҢETжүҖеҝ…йңҖзҡ„дёҚеҗҢд»ӘеҷЁиҝӣиЎҢеҗҢжӯҘгҖӮжңҖдёәйҮҚиҰҒзҡ„жҳҜпјҢеҝ…йЎ»д»ҘжңҖдҪҺзЁӢеәҰзҡ„жҠ–еҠЁеҗҢжӯҘRFдҝЎеҸ·еҸ‘з”ҹеҷЁе’ҢеҹәеёҰд»»ж„ҸжіўеҪўеҸ‘з”ҹеҷЁ(AWG)гҖӮжӯӨеӨ–пјҢе®ғеҝ…йЎ»иғҪеӨҹд»Ҙж¬Ўзәіз§’зҡ„зІҫеәҰеҒҸ移еҹәеёҰеҢ…з»ңзӣёеҜ№дәҺRFжіўеҪўзҡ„延иҝҹгҖӮеҰӮжһңдҪҝз”Ёдј з»ҹеҸ°ејҸд»ӘеҷЁпјҢиҰҒе®һзҺ°иҝҷдёҖзЁӢеәҰзҡ„еҗҢжӯҘжҳҜйқһеёёеӣ°йҡҫзҡ„пјҢиҖҢдё”иҝҳеҫҲжңүеҸҜиғҪдјҡж¶үеҸҠдёҚеҗҢеҺӮе•Ҷзҡ„硬件пјҢдҪҝеә”з”ЁиҪҜ件еҸҳеҫ—жӣҙеӨҚжқӮгҖӮ

NIз®ҖеҢ–дәҶеҗҢжӯҘй—®йўҳпјҢ并е°ҶиҪҜ硬件йӣҶжҲҗеҲ°дёҖдёӘе№іеҸ°дёҠпјҢд»ҺиҖҢе°ҪеҸҜиғҪең°дҪҝиҜҘжөҒзЁӢеҸҳеҫ—з®ҖеҚ•жҳҺдәҶгҖӮPXIиғҢжқҝпјҲи§Ғеӣҫ4пјүеҸҜз”ЁдәҺи·Ҝз”ұжңәз®ұеҶ…е®һзҺ°еҗҢжӯҘжүҖйңҖзҡ„жүҖжңүж—¶й’ҹе’Ңи§ҰеҸ‘зәҝпјҢеӣ иҖҢж— йңҖеӨ–йғЁж—¶й’ҹе’Ңи§ҰеҸ‘жқҘи·Ҝз”ұзҪ‘з»ңгҖӮдёәдәҶе®һзҺ°ж¬Ўзәіз§’зә§зҡ„еҗҢжӯҘе’ҢеҸҜйҮҚеӨҚжҖ§пјҢйҮҮз”ЁNI-TCLKжқҘеҚҸи°ғеӨҡдёӘжЁЎеқ—еҢ–д»ӘеҷЁй—ҙзҡ„ж—¶й’ҹе’Ңи§ҰеҸ‘еҲҶеёғгҖӮеҰӮйңҖиҜҰз»ҶдәҶи§ЈNI-TClkеҰӮдҪ•д»ҘдҪҺиҫҫ20psrmsзҡ„жҠ–еҠЁжқҘеҗҢжӯҘеӨҡдёӘд»ӘеҷЁпјҢиҜ·йҳ…иҜ»NI T-ClockжҠҖжңҜз”ЁдәҺжЁЎеқ—еҢ–д»ӘеҷЁе®ҡж—¶е’ҢеҗҢжӯҘгҖӮ

еӣҫ4. еӣҫдёәPXI ExpressиғҢжқҝд»ҘеҸҠж—¶й’ҹе’Ңи§ҰеҸ‘еҺҹзҗҶеӣҫгҖӮ

жңҖеҗҺпјҢNIзҡ„еҗ„з§ҚжЁЎеқ—еҢ–д»ӘеҷЁдә§е“ҒеҸҜз”ЁдҪңдёәе…·жңүETеҠҹиғҪзҡ„RF PAжөӢиҜ•и®ҫзҪ®зҡ„жҜҸдёҖдёӘ组件гҖӮжӮЁд№ҹеҸҜе°Ҷе®Ңж•ҙзҡ„PAжөӢиҜ•зі»з»ҹйӣҶжҲҗеҲ°дёҖдёӘPXIжңәз®ұе’Ңз»ҹдёҖзҡ„硬件й©ұеҠЁAPIйӣҶеҗҲпјҢиҝҷеҸҜжһҒеӨ§з®ҖеҢ–зі»з»ҹзҡ„йӣҶжҲҗе’ҢжөӢиҜ•ејҖеҸ‘гҖӮ

1. NIжөӢиҜ•и§ЈеҶіж–№жЎҲ

硬件и®ҫзҪ®

еҰӮжһңиҰҒеҜ№ж ҮеҮҶPAжөӢиҜ•и§ЈеҶіж–№жЎҲиҝӣиЎҢж”№иүҜд»ҘйҖӮеә”ETжөӢиҜ•пјҢеҝ…йЎ»еңЁзі»з»ҹдёӯж·»еҠ AWGпјҲи§Ғеӣҫ3пјүгҖӮAWGеҝ…йЎ»иғҪеӨҹй©ұеҠЁеҚ•з«Ҝе’Ңе·®еҲҶиҙҹиҪҪпјҢеә”з”Ёеёёи§ҒжЁЎејҸе’Ңеҫ®еҲҶзӣҙжөҒеҒҸ移гҖҒеҸҜеҸҳеўһзӣҠи®ҫзҪ®д»ҘеҸҠзҒөжҙ»зҡ„ж—¶й’ҹйҖүйЎ№гҖӮNI PXIe-5451жҳҜдёҖж¬ҫеҸҜж»Ўи¶іжүҖжңүиҝҷдәӣйңҖжұӮзҡ„400 MS/sеҸҢйҖҡйҒ“AWGгҖӮе®ғиҝҳеҢ…еҗ«и®ёеӨҡжқҝиҪҪдҝЎеҸ·еӨ„зҗҶеҮҪж•°пјҢе…¶дёӯеҢ…жӢ¬з”ЁдәҺи„үеҶІж•ҙеҪўе’ҢжҸ’еҖјзҡ„и„үеҶІе“Қеә”(FIR)ж»ӨжіўгҖҒе№іеқҰеәҰж ЎжӯЈд»ҘеҸҠеҸҜеҮҸе°‘иҪҜ件预еӨ„зҗҶзҡ„ж•°еӯ—дёҠеҸҳйў‘еҷЁгҖӮ

еңЁиҜҘеә”з”ЁдёӯдҪҝз”Ёзҡ„RFдҝЎеҸ·еҸ‘з”ҹеҷЁжҳҜ6.6 GHz NI PXIe-5673EзҹўйҮҸдҝЎеҸ·еҸ‘з”ҹеҷЁ(VSG)пјҢе…¶еёҰе®Ҫи¶…иҝҮ100 MHzгҖӮNI PXIe-5673EжҳҜз”ұдёүдёӘзӢ¬з«Ӣзҡ„жЁЎеқ—з»„жҲҗпјҡNI PXIe-5450д»»ж„ҸжіўеҪўеҸ‘з”ҹеҷЁгҖҒNI PXIe-5652жң¬ең°жҢҜиҚЎеҷЁе’ҢNI PXIe-5611 I/QзҹўйҮҸи°ғеҲ¶еҷЁгҖӮ

еӣҫ5. NI PXIe-5673E VSGзҡ„жӯЈйқўеӣҫеұ•зӨәдәҶдёүдёӘзӢ¬з«Ӣзҡ„жЁЎеқ—гҖӮ

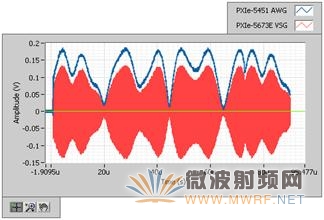

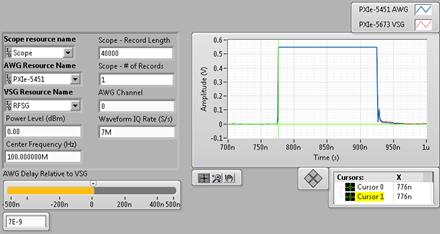

еӣҫ6жҳҫзӨәзҡ„жҳҜйӘҢиҜҒVSGе’ҢAWGеҗҢжӯҘе’ҢйҮҚеӨҚжҖ§жүҖдҪҝз”Ёзҡ„и®ҫзҪ®гҖӮNI PXIe-5673E VSGз”ЁдәҺз”ҹжҲҗRFжіўеҪўпјҢNI PXIe-5451з”ЁдәҺз”ҹжҲҗеҹәеёҰеҢ…з»ңжіўеҪўгҖӮNI PXIe-5154 1 GHzж•°еӯ—еҢ–д»Әз”ЁдәҺеҗҢжӯҘйӘҢиҜҒпјҢдҪҶд№ҹеҸҜдҪҝз”Ёд»»дҪ•е…·жңүи¶іеӨҹй«ҳйҮҮж ·зҺҮе’ҢеёҰе®Ҫзҡ„зӨәжіўеҷЁгҖӮ

еӣҫ6. иҜҘжөӢиҜ•и®ҫзҪ®йӘҢиҜҒдәҶAWGе’ҢVSGжҳҜеҗҢжӯҘзҡ„гҖӮ

дёәдәҶеҗҢжӯҘAWGе’ҢVSGпјҢдёӨдёӘи®ҫеӨҮеҝ…йЎ»е…ұдә«еҗҢдёҖдёӘ10 MHzеҸӮиҖғж—¶й’ҹгҖӮеҸӮиҖғж—¶й’ҹзҡ„жқҘжәҗеҸҜд»ҘжҳҜNI PXI 10 MHzиғҢжқҝж—¶й’ҹпјҢд№ҹеҸҜд»ҘжҳҜеӨ–йғЁжҸҗдҫӣзҡ„10 MHzж—¶й’ҹгҖӮ

иҪҜ件

еӣҫ7жҳҫзӨәзҡ„жҳҜз”ҹжҲҗе®һзҺ°ETжүҖйңҖзҡ„RFе’ҢеҢ…з»ңжіўеҪўжүҖеҝ…йңҖзҡ„иҪҜ件жӯҘйӘӨгҖӮиҰҒз”ҹжҲҗзҡ„LTEжіўеҪўеҸҜдҪҝз”ЁNI LTEе·Ҙе…·еҢ…жқҘеҲӣе»әпјҢжҲ–д»Һж–Ү件дёӯиҜ»еҸ–гҖӮ然еҗҺдҫҝеҸҜи®Ўз®—еҢ…з»ңжіўеҪўпјҢеҢ…з»ңжіўеҪўжҳҜLTEжіўеҪўзҡ„дёҖдёӘеҮҪж•°гҖӮжӮЁд№ҹи®ёиҝҳеёҢжңӣиҝӣиЎҢдёҖдәӣйўқеӨ–зҡ„дҝЎеҸ·еӨ„зҗҶпјҢжҜ”еҰӮж•°еӯ—йў„еӨұзңҹжҲ–е…¶д»–ж»Өжіўж“ҚдҪңжқҘдјҳеҢ–з”ЁдәҺETзҡ„жіўеҪўгҖӮеҸҜеҜ№VSGиҝӣиЎҢй…ҚзҪ®жқҘз”ҹжҲҗLTEжіўеҪўпјҢNI PXIe-5451зҡ„й…ҚзҪ®дёҺNI PXIe-5673E VSGдёӯзҡ„NI PXIe-5450 AWGзӣёдјјпјҲи§Ғеӣҫ5пјүгҖӮжҺҘзқҖеҢ…з»ңжіўеҪўдҫҝеҸҜзӣёеҜ№RFжіўеҪўиҝӣиЎҢ时移пјҢ并дёҺз”ЁдәҺжҺ§еҲ¶жіўеҪўз”ҹжҲҗзҡ„硬件и„ҡжң¬дёҖиө·еҶҷе…ҘеҲ°жқҝиҪҪеҶ…еӯҳдёӯгҖӮпјҲжҹҘзңӢдёӢйқўе…ідәҺ“жіўеҪўз”ҹжҲҗ延иҝҹе®һзҺ°”зҡ„еҶ…е®№пјҢдәҶи§ЈеҢ…з»ңжіўеҪўж—¶з§»з®—жі•гҖӮпјүжңҖеҗҺпјҢеӨҡдёӘи®ҫеӨҮеҸҜйҖҡиҝҮTClkжқҘиҝӣиЎҢеҗҢжӯҘе’ҢеҲқе§ӢеҢ–гҖӮ

еӣҫ7. еӣҫдёәз”ҹжҲҗETжүҖйңҖзҡ„RFе’ҢеҢ…з»ңжіўеҪўжүҖеҝ…йңҖзҡ„иҪҜ件жөҒзЁӢз®ҖеӣҫгҖӮ

еҗҢжӯҘеҹәеёҰеҢ…з»ңеҸ‘з”ҹеҷЁе’ҢRFдҝЎеҸ·еҸ‘з”ҹеҷЁжүҖйңҖзҡ„иҪҜ件зӣёеҜ№з®ҖеҚ•гҖӮVSGе’ҢAWGе…ұдә«еҗҢдёҖеҸӮиҖғж—¶й’ҹеҗҺпјҢNI-TClkдҫҝеҸҜз”ЁдәҺеҗҢжӯҘзҺҜиҠӮгҖӮжӯӨж—¶пјҢеҜ№AWGе’ҢVSGз”ҹжҲҗзҡ„жіўеҪўиҝӣиЎҢзӣёдҪҚй”Ғе®ҡпјҢдёӨдёӘжіўеҪўд№Ӣй—ҙеӯҳеңЁеҸҜйҮҚеӨҚ延иҝҹгҖӮиҜҘ延иҝҹжҳҜз”ұдәҺNI-TClkжІЎжңүи®Ўз®—NI PXIe-5450 AWGеҲ°NI PXIe-5611 I/Qи°ғеҲ¶еҷЁд№Ӣй—ҙзҡ„жЁЎжӢҹи·Ҝеҫ„иҖҢдә§з”ҹзҡ„пјҲиҜҰи§Ғеӣҫ5пјүгҖӮз”ұдәҺиҜҘ延иҝҹдёәеёёж•°пјҢеӣ жӯӨеҸҜйҖҡиҝҮи®ҫзҪ®AWGзӣёеҜ№дәҺVSGзҡ„延иҝҹжқҘиҝӣиЎҢж¶ҲйҷӨгҖӮеҜ№дәҺи®ёеӨҡETеә”з”ЁпјҢAWGзӣёеҜ№дәҺVSGзҡ„延иҝҹпјҲжҲ–VSGзӣёеҜ№дәҺAWGзҡ„延иҝҹпјүеҜ№дәҺжүҫеҲ°е»¶иҝҹдјҳеҢ–и®ҫеӨҮжҖ§иғҪиҮіе…ійҮҚиҰҒгҖӮиҜҘ延иҝҹеҝ…йЎ»жҳҜеҸҜйҮҚеӨҚзҡ„пјҢдё”е…·жңүжңҖдҪҺзЁӢеәҰзҡ„жҠ–еҠЁпјҢиҝҷжҳҜеӣ дёәе°ұ算延иҝҹеҸӘеҒҸзҰ»жңҖдҪіеҖјеҮ зәіз§’пјҢд№ҹдјҡдҪҝи®ҫеӨҮзҡ„зәҝжҖ§еәҰеҮҸе°‘иӢҘе№ІдёӘdBгҖӮ

жіўеҪўз”ҹжҲҗ延иҝҹе®һзҺ°

и®°дҪҸпјҡVSGе’ҢAWGд№Ӣй—ҙзҡ„延иҝҹжҺ§еҲ¶еҜ№дәҺETиҠҜзүҮжөӢиҜ•е’Ңзү№жҖ§и®°иҝ°жҳҜиҮіе…ійҮҚиҰҒзҡ„гҖӮиҜҘ延иҝҹеҸҜйҖҡиҝҮеңЁзЎ¬д»¶дёӯж·»еҠ зӯүеҫ…йҮҮж ·е’ҢеҒҸ移йҮҮж ·ж—¶й’ҹжҲ–йҖҡиҝҮеңЁиҪҜ件дёӯдҪҝз”ЁDSPжқҘе®һзҺ°гҖӮиҷҪ然еңЁзЎ¬д»¶дёӯеҸҜе®һзҺ°иҜҘ延иҝҹпјҢдҪҶжҳҜе®ғйңҖиҰҒETжіўеҪўйҮҚж–°йҮҮж ·иҮі200 MHzжүҚиғҪжҢҮе®ҡзәіз§’зә§еҲҶиҫЁзҺҮзҡ„延иҝҹгҖӮз”ұдәҺ并йқһжҜҸдёӘз”ЁжҲ·йғҪиғҪеӨҹеҜ№жіўеҪўиҝӣиЎҢйҮҚж–°йҮҮж ·пјҢеӣ жӯӨжҲ‘们жӣҙеҖҫеҗ‘дәҺеңЁиҪҜ件дёӯе®һзҺ°е»¶иҝҹгҖӮ

иҪҜ件延иҝҹз®—жі•йҮҮз”Ёзҡ„жҳҜзҰ»ж•ЈеӮ…йҮҢеҸ¶еҸҳжҚў(DFT)时移е®ҡзҗҶпјҢиҜҘе®ҡзҗҶжҳҜжҢҮйҖҡиҝҮndж¬ЎйҮҮж ·жқҘ延иҝҹе‘Ёжңҹж—¶еҹҹжіўеҪўпјҢе…¶DFTе°Ҷдјҡд»Ҙзі»ж•° еҸҳеҢ–,е…¶дёӯkжҳҜзҰ»ж•Јйў‘зҺҮжҢҮж•°гҖӮ

еҸҳеҢ–,е…¶дёӯkжҳҜзҰ»ж•Јйў‘зҺҮжҢҮж•°гҖӮ

жӮЁиҝҳеҸҜдҪҝз”ЁиҜҘз»“жһңйҖҡиҝҮx[n]ж¬ЎйҮҮж ·жқҘ延иҝҹndпјҢж“ҚдҪңжӯҘйӘӨеҰӮдёӢпјҡ

1. еҸ–x[n]дёӯзҡ„NдёӘзӮ№пјҢеҫ—еҲ°X[k]пјҢ0≤k≤N-1

2. X[k]д№ҳд»Ҙ пјҢ0≤k≤N-1

пјҢ0≤k≤N-1

3. е°Ҷеҫ—еҲ°зҡ„з»“жһңиҝӣиЎҢзҰ»ж•ЈеӮ…йҮҢеҸ¶йҖҶеҸҳжҚў

2. з»“жһң

еңЁNI LabVIEWзі»з»ҹи®ҫи®ЎиҪҜ件е’ҢANSI CдёӯеқҮйҷ„жңүз”ЁдәҺеҗҢжӯҘжіўеҪўе№¶еҸҜи®©з”ЁжҲ·иғҪеӨҹе®һзҺ°дёҖдёӘжіўеҪўзӣёеҜ№еҸҰдёҖдёӘжіўеҪўзҡ„зҡ®з§’зә§еҲҶиҫЁзҺҮ延иҝҹзҡ„иҢғдҫӢд»Јз ҒгҖӮйЎ№зӣ®иҢғдҫӢдҪҚдәҺжң¬ж–Үз»“е°ҫеӨ„гҖӮеӣҫ9 жҳҫзӨәзҡ„жҳҜдҪҝз”ЁNI PXIe-5154 1 GHzж•°еӯ—еҢ–д»ӘиҝӣиЎҢж•°жҚ®йҮҮж ·зҡ„LabVIEWйҮҮж ·д»Јз Ғзҡ„е…ёеһӢз»“жһңгҖӮеңЁжң¬иҢғдҫӢдёӯпјҢеҹәеёҰеҢ…з»ңдҝЎеҸ·д»…дёәз»ҸжҚўз®—зҡ„LTEжіўеҪўе№…еәҰгҖӮд»ҺеӣҫдёӯжҲ‘们еҸҜд»ҘзңӢеҮәеҹәеёҰеҢ…з»ңдёҺRFжіўеҪўжҳҜдёҖиҮҙзҡ„гҖӮ

еӣҫ9. RF LTEжіўеҪўдёҺеҹәеёҰеҢ…з»ң

еӣҫ10жҳҫзӨәзҡ„жҳҜLabVIEW ETжј”зӨәж“ҚдҪңзҡ„еүҚйқўжқҝз•ҢйқўгҖӮйҷӨдәҶдёҖдәӣж ҮеҮҶзҡ„硬件иө„жәҗжҺ§д»¶еӨ–пјҢиҝҳжңүе…¶д»–дёҖдәӣеҸӮж•°д№ҹеҖјеҫ—иҜҙжҳҺдёҖдёӢгҖӮйҰ–е…ҲжҳҜжіўеҪўIQзҺҮгҖӮжң¬ж“ҚдҪңжј”зӨәдёӯпјҢеҒҮе®ҡRFе’ҢеҢ…з»ңжіўеҪўеқҮд»ҘзӣёеҗҢзҡ„йҖҹзҺҮйҮҮж ·пјҢйҖҹзҺҮеҸҜд»ҘжҳҜд»»ж„ҸеҖјгҖӮд№ӢеүҚжҲ‘们讨и®әзҡ„пјҢеҰӮжһңиҰҒд»Ҙд»»ж„ҸйҮҸ延иҝҹеҢ…з»ңе’ҢRFжіўеҪўпјҢдёӨдёӘжіўеҪўеқҮиҰҒд»Ҙ200 MHzзҡ„йў‘зҺҮйҮҚж–°йҮҮж ·гҖӮ第дәҢдёӘйҮҚиҰҒеҸӮйҮҸжҳҜжҳҜAWGзӣёеҜ№VSGзҡ„延иҝҹжҺ§д»¶гҖӮжҺ§д»¶е®һйҷ…дёҠз”ЁдәҺжҺ§еҲ¶еҢ…з»ңзӣёеҜ№дәҺRFжіўеҪўзҡ„延иҝҹпјҢеҸҜйҖҡиҝҮиҫ“е…ҘиҙҹеҖјжқҘжҺ§еҲ¶RFжіўеҪўзӣёеҜ№дәҺеҢ…з»ңзҡ„延иҝҹгҖӮ

д»Һеӣҫ9зҡ„RFе’ҢеҢ…з»ңжіўеҪўдёӯ,жҲ‘们еҫҲйҡҫзЎ®е®ҡзІҫеәҰдёәзәіз§’зә§зҡ„жіўеҪўе»¶иҝҹжҳҜеҗҰдёҺйў„жңҹдёҖиҮҙгҖӮеӣҫ10дёӯзҡ„жіўеҪўеӣҫжҳҫзӨәзҡ„жҳҜдёҖдёӘRFе’ҢеҢ…з»ңжіўеҪўиҢғдҫӢеҜјеҮәзҡ„ж•°еӯ—еҢ–ж Үи®°дәӢ件гҖӮдҪҝз”Ёж Үе°әпјҢеҸҜд»ҘзңӢеҲ°пјҢRFжіўеҪўзӣёеҜ№дәҺеҢ…з»ң延иҝҹдәҶ7 nsпјҢиҝҷдё»иҰҒжҳҜз”ұдәҺNI PXIe-5611дёҠеҸҳйў‘еҷЁзҡ„и·Ҝеҫ„延иҝҹе’Ңз”өзјҶй•ҝеәҰе·®ејӮгҖӮеҰӮжһңиҰҒдҪҝдёӨдёӘжіўеҪўе®Ңе…ЁйҮҚеҸ пјҢеҲҷAWGзӣёеҜ№дәҺVSGжҺ§д»¶еә”и®ҫзҪ®дёә7 nsпјҢеҰӮеӣҫ11жүҖзӨәгҖӮ

еӣҫ10. LabVIEW ETжј”зӨәж“ҚдҪңеүҚйқўжқҝ: ж Үи®°дәӢ件д»ҺVSGе’ҢAWGдёӯеҜјеҮәгҖӮдҪҝз”Ёж Үе°әпјҢеҸҜд»ҘзңӢеҲ°RFжіўеҪўзӣёеҜ№дәҺAWG延иҝҹдәҶ7 nsгҖӮ

еӣҫ11. RFжіўеҪўе’ҢеҢ…з»ңжіўеҪўд№Ӣй—ҙзҡ„7 ns延иҝҹеҸҜйҖҡиҝҮ延иҝҹAWG 7 nsиҝӣиЎҢиЎҘеҒҝгҖӮ

дҪҝз”Ёдј з»ҹзҡ„зӣҙжөҒз”өжәҗдјҡж¶ҲиҖ—еӨ§йҮҸзҡ„з”өиғҪпјҢиҝҷдҪҝеҫ—еҜ№дәҺLTEеҠҹзҺҮж”ҫеӨ§еҷЁиҖҢиЁҖпјҢETжҖ§иғҪе°ұеҸҳеҫ—иҮіе…ійҮҚиҰҒгҖӮиҷҪ然иҜҘжҠҖжңҜжңүжңӣжҳҫзқҖжҸҗй«ҳPAж•ҲзҺҮпјҢдҪҶжҳҜдҝ®ж”№зҺ°жңүжөӢиҜ•е’Ңзү№жҖ§и®°иҝ°и®ҫзҪ®жқҘйҖӮеә”ETжҳҜдёҖ件йқһеёёеӣ°йҡҫдё”жҲҗжң¬дёҚиҸІзҡ„жҢ‘жҲҳгҖӮеҖҹеҠ©NIе№іеҸ°е’Ңжң¬ж–ҮжҸҗдҫӣзҡ„йҮҮж ·д»Јз ҒпјҢжӮЁеҸҜд»ҘеҜ№зҺ°жңүNI PXIеҠҹзҺҮж”ҫеӨ§еҷЁжөӢиҜ•з«ҷиҝӣиЎҢж”№иҝӣпјҢд»Ҙж”ҜжҢҒETпјҢдё”жүҖиҠұиҙ№зҡ„жҲҗжң¬е’Ңж—¶й—ҙиҝңдҪҺдәҺдј з»ҹеҸ°ејҸи®ҫеӨҮжүҖиҰҒжұӮзҡ„гҖӮ

жқҘжәҗпјҡNIдҫӣзЁҝ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·