屏蔽壳常用于保护微波印刷电路板(PCB)。屏蔽壳在保护PCB免受环境影响的同时,也会改变电路的电气性能。如果了解屏蔽壳的影响以及如何预测这些影响,就能提高大多数现代计算机辅助工程(CAE)仿真工具的精度。本系列文章分两部分,通过对频率、位置、以及屏蔽壳感应共振模式的本质特征的精确预测,可以将屏蔽壳的影响降至最低,其技巧在第一部分作了概括。

避免不想要的共振模式的关键之一包括了解最大电场(E)和磁场(H)的知识,以及两者相应的共振频率。对PCB电路仔细进行布局和布线可大大减少共振模式的影响。为论证这一方法,在屏蔽体附近放置了两个滤波器,将第一个滤波器(A滤波器)置于屏蔽体中心位置,结果产生具有E场热区及在4.1、7.2和8.3 GHz频率处有预期场激励的TM110、TM210和TM310模式。

相反,第二个滤波器(B滤波器)向屏蔽腔底部放置。在这一区域,场强非常小,共振影响预期比第一个滤波器产生的影响小。用Ansoft HFSS 电磁(EM)软件仿真也预测到对于B滤波器那样的放置共振影响要小许多(见图1)。

另一个例子给出了一个电路与另一个电路不希望的耦合产生的影响(图2)。连接到端口1到端口2的电路包括一根接地的微带短截线,接到端口3到端口4的电路是一个阶跃阻抗微带低通滤波器。对表中描述的全部5种模式,两个电路都在高H场附近。因此,我们应能预料到在4.2、 5.9、7.2、8.0和8.3 GHz频率下有共振效应。出现在端口3的端口1的能量曲线图如图3示。注意:在预测的共振频率处,有5个传输相当高的峰值。

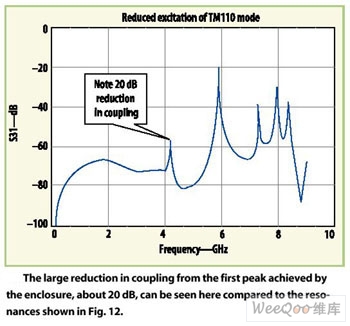

如果将相同的电路移入屏蔽壳内(见图4),将单接地的短截线置于TM110模式的H场零点,预期这一模式激励应该会降低(见图4)。

其余峰值仍然明显,因为TM110模式下H场零点位置实际上是另一种模式下屏蔽体内部的高或者甚至最大的H场*点。

以上简单仿真用于证明屏蔽体内部RF电路的布局和布线会影响共振模式下的激励程度。此外,从上面E场和 H场曲线图可以看出,如果激励高阶模式,则整个屏蔽体变热非常快,所以,选择电路布放来减小共振模式激励可能还有相当大的争议。

最后,再强调也不过分的一点是电路的有效布局只能减少共振影响,但确实不能完全消除这些影响。消除这些会带来问题的共振的唯一办法就是改变屏蔽体尺寸,使共振频率远离设计中存在的任何频率,或者使用RF吸收器,实际上也是改变屏蔽壳的尺寸。

这里给出的信息只是一般概括,用于分解和解决会困扰RF设计的屏蔽腔共振问题。用此处给出的简单公式可以粗略估计共振模式的频率。主要和次要模式热区应该在设计之前就确定,这样可避免激励起不希望的模式这一缺陷。应该确定最佳屏蔽尺寸,降低屏蔽共振的影响。此外,这里给出的信息应该能帮助工程师发现并排除现有设计存在的屏蔽共振问题,也是一种辨别RF吸收器或金属支撑杆的布放位置以消除共振模式的工具。

粤公网安备 44030902003195号

粤公网安备 44030902003195号