高性能的无线通信对系统有非常严格的需求,主要是以下三个方面:

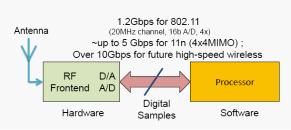

1.高速的系统吞吐量

包括远端射频头和PHY层协议之间以及PHY层协议内部的模块之间。例如,实现802.11系列协议,单天线需要大约1.2Gbps的吞吐量,如果支持4x4 MIMO应用,那么至少5Gbps以上,这个指标目前对大部分PC都是严峻的挑战。

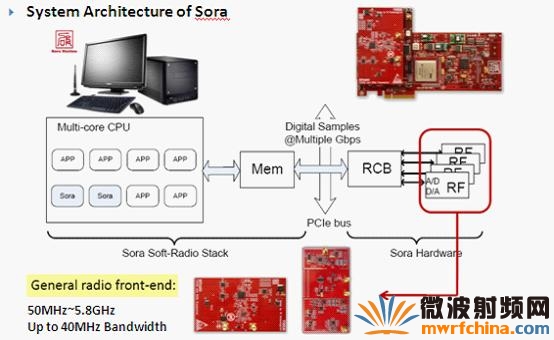

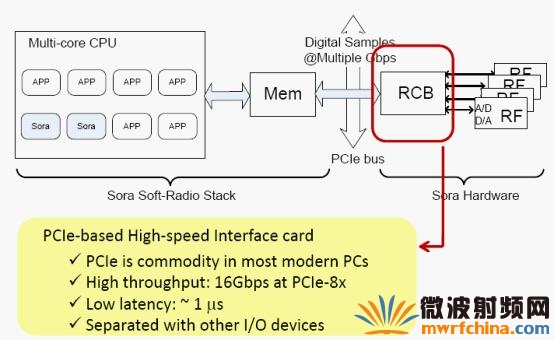

Sora的硬件架构

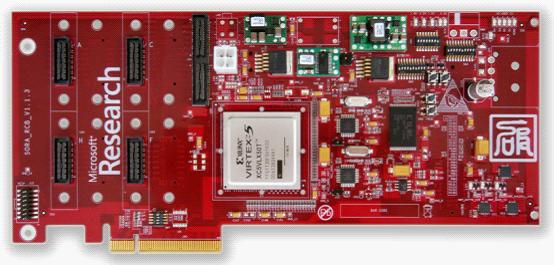

Radio Control Board:RCB

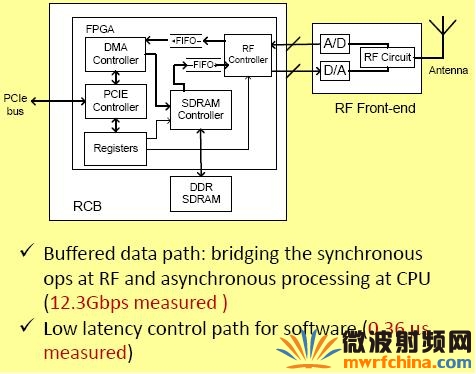

RCB是Sora系统的核心板卡,采用了PCI Express 8x架构,最高吞吐率达到16Gbps。RCB上有8个通用的射频接口,可以支持最高8x8MIMO。FPGA内容逻辑框图如下:

Radio Adapter Board:RAB

实现ADC和DAC功能,将模拟基带转换为数字基带信号。采用USRP兼容的接口,可以支持Ettus公司大部分射频模块。双通道ADC,12位64MSPS以及双通道DAC,14位64MSPS。板上FPGA提供参考设计代码

Radio Module:

实现天线接口和上下变频,将射频芯片转换为模拟基带,频率范围覆盖WiFi、LTE和WiMax等主要通信频段,带宽最高可达80MHz。

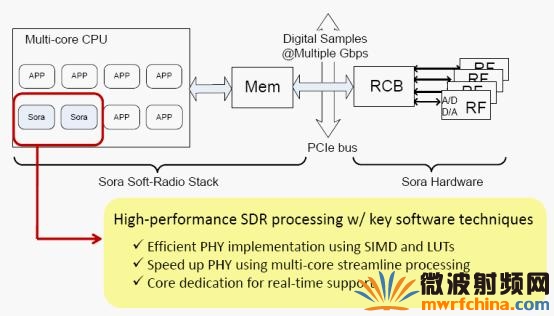

Sora的软件架构

主要技术:

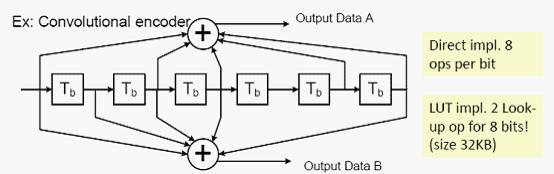

1. 采用查找表技术充分利用CPU的L2 Cache, 大部分的PHY层算法可以通过查找表来加速1.5~22倍。

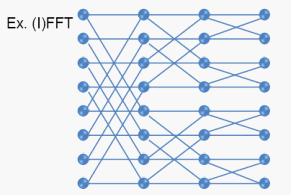

2. SIMD指令集优化。充分利用CPU并行加速指令,特别适合FFT和IFFT这一类运算。

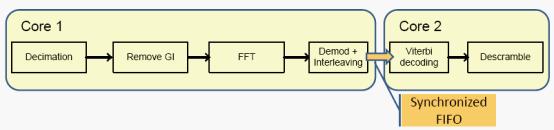

3. 利用多核流水线技术

通过同步FIFO,将PHY层实现的子流水线模块分配到不同的内核执行,充分利用多核

CPU的计算能力。

4. 独占内核技术

为了确保CPU可以实时响应,Sora采用了独占线程技术,可以让某个或者某几个内核专用于SDR的任务,不被其他系统调用影响。 实现这种技术不需要修改操作系统的内核。

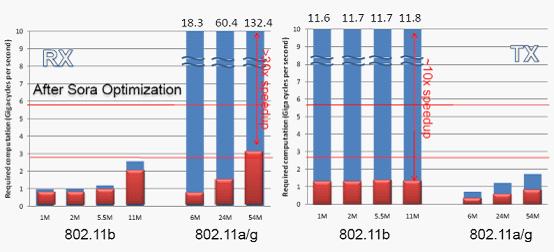

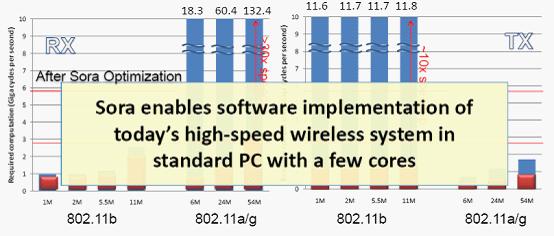

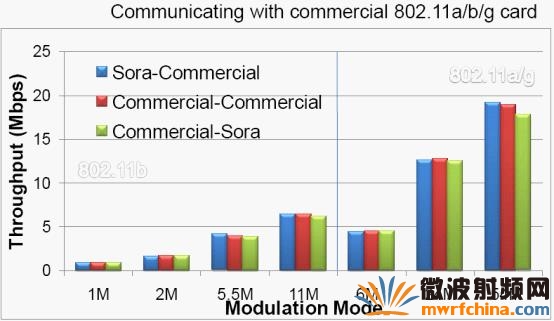

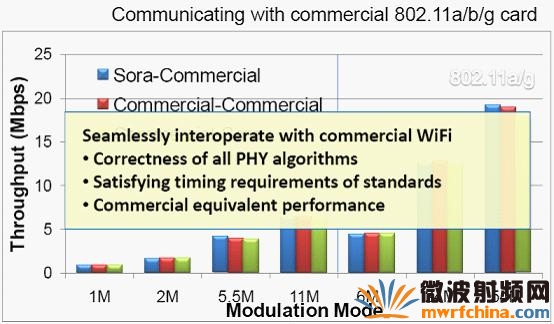

Sora的性能测试

以WiFi 802.11a/b/g的实现为案例,测试Sora的性能。算法优化前后对比

Sora与商业网卡吞吐量对比

SoraSDK开发包

Sora学术套件提供了SDK开发包,提供了开源实现的802.11a/b/g的PHY和MAC实现。自从2010年发布以来,多次更新,目前的版本为SDK1.6,下载链接如下:

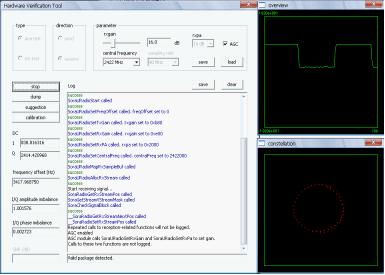

SDK不仅提供了PHY和MAC的实现代码,还提供了调试用的一些工具,如示波器

粤公网安备 44030902003195号

粤公网安备 44030902003195号