1 引言

软件无线电主要由天线、射频前端、宽带A/D和D/A转换器、数字信号处理器(DSP)及各种软件组成。软件无线电体系结构的一个重要特点是将A/D和D/A尽量靠近射频前端。为减少模拟环节,在较高的中频、甚至直接对射频信号进行数字化,后面所有功能都由软件或数字硬件实现。软件无线电通信系统要求ADC具有高速度、高精度和宽带输入信号范围。

主要依靠一揽子电阻网络来保证量化精度的传统ADC,其精度不可能做得很高,其高端的非线性难以避免。那么,能不能减轻对电阻网络的依赖转而依靠数字信号处理技术来提高精度呢?答案是肯定的,但必须减少量化的带内噪声。于是,Σ-Δ ADC和Σ-Δ DAC便应运而生了。

Σ-Δ A/D转换技术的实质是尽量降低模拟电路的复杂程度,减少带内的量化噪声,然后采用数字信号处理和VLSI技术相结合的方法来提高信号处理精度,增加动态范围。下面详细讨论Σ-Δ A/D转换技术。

2 Σ-Δ A/D转换技术

2.1 Σ-Δ A/D转换器的基本原理

2.2.1 A/D转换中的混叠噪声和量化噪声

一般认为,传统ADC的量化噪声可作如下近似:

![]()

其中,q为量化台阶,b为量化位数。相应的噪声谱密度为:

![]()

可见,量化位数b越多,量化噪声功率越小,采样频率fs越高,分布在基带内的噪声越少。

2.2.2 低通Σ-Δ A/D转换器的基本原理

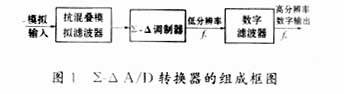

低通Σ-Δ A/D量化是在量化的基础上发展而来的,Σ-Δ ADC组成框图如图1所示。

它与传统A/D转换器的最大不同在于量化过程。后者取样与量化值是一一对应的,而前者几乎完全抛开了这一点。

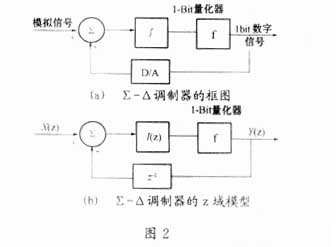

图2 (a)是一个典型的Σ-Δ低通调制器的原理框图,图2(b)是Σ-Δ低通调制器的Z域模型。

待量化的模拟信号与Σ-Δ调制后的1bit输出信号相差后,送到积分器中,进行1bit量化,从而得到采样率为fs的1bit流,该1bit流包含了原始模拟信号的大部分特性。随后,系统把该1bit流送给后面的数字抽取器,由数字抽取器从这些粗糙的量化数据中重构出低采样率的高分辨率数字信号。由于该方法采用1bit量化,因而硬件结构简单。由于采样频率很高,因而对前端模拟抗混叠滤波器的要求大大降低。而这两方面的因素正是解决传统A/D转换器分辨率难以提高的关键。对传统的并行A/D转换器而言,采样频率每增加一倍,信噪比改善约为3dB,相当于0.5位的量化位数。而Σ-Δ转换器则为:采样频率每增加一倍,信噪比改善约为9dB,相当于1.5位的量化位数。这就是说,要达到相的量化信噪比,Σ-Δ转换器与普通A/D转换器相比,所需的采样率要低得多。

归纳起来,Σ-Δ调制器性能主要得益于过采样(Oversampling)、噪声整形(Noise Shaping)及抽取(Decimation)。

(1)过采样

过采样是Σ-Δ调制器以速度换精度的前提。过采样带来的好处是:减少了基带内的量化噪声。由式(1),分布在基带内的噪声功率为:

![]()

一般地,fb≤fs,因此,基带内的噪声能量被大大降低。应该指出,这只是在不计Σ-Δ调制的情况下,仅由采样率fs提高带来的量化噪声减小。如果计及由Σ-Δ调制带来的量化噪声向高频端的推移,则基带噪声功率会进一步减小。

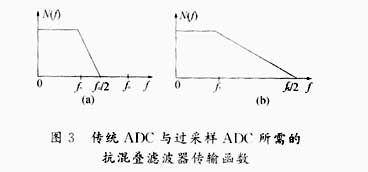

过采样带来的另一个好处是:降低了对前端抗混叠模拟滤波器的要求。传统ADC与过采样ADC所需的抗混叠滤波器传输函数分别如图3(a)和图3(b)所示。

传统ADC的防混滤波器过渡带为fn/2-fb,而过采样ADC的防混滤波器过渡带为fs/2-fb, 但fsfb,故,过采样ADC的防混滤波器过渡带比传统ADC的宽很多。既然过渡带与通带之比决定了滤波器的复杂性,因此,过采样ADC对防混滤波器的要求非常简单。例如,对fs/fn=64,一个简单的RC低通滤波器就足够了。

(2)噪声整形

噪声整形是Σ-Δ调制器提高输出SNR(信噪比)的关键。Σ-Δ调制器能将低频量化噪声调制到高频段,改变噪声分布,这就是噪声整形的由来。

噪声整形大大增加了过采样效果,即用提高工作采样频率换取量化精度的效果。因此,只要滤除了带外的量化噪声,就能够从1bit流中有效地用速度换取精度。这正是Σ-Δ转换器获取高分辨率的原理所在。

(3) 数字抽取

滤除将要折叠到基带中的噪声是数字滤波级的主要任务,去除量化噪声也就相当于提高了数字输出的有效精度,即把1bit数据重构成多bit数据。同时,它还要把过高的采样率降下来。

调制器的输出是模拟输入的粗糙量化。然而,调制器是在奈奎斯特频率的N倍上进行采样的。故,高精度可以通过平均这N个点而获得。平均过程相当于频域的低通滤波。其抽取过程可按图4进行。

用单一系数的梳状滤波器作抽取器的第一级可以极大地节约时间,但是,它并不能有效去除大部分带外量化噪声,因此,实用中都需再加一个FIR数字滤波器。

这样,过采样、噪声整形和数字滤波方法的有机结合就可以克服现有VLSI技术难以制作噪声容限小的模拟电路之不足,在无需附加工艺的情况下,利用元件精度和匹配要求低的“Σ-Δ量化器”来实现高分辨率的A/D转换。

3 高阶Σ-Δ A/D转换技术

Σ-Δ A/D转换器的基带噪声比奈奎斯特采样器或Δ调制器的要小得多。但是,对前述的一阶Σ-Δ调制器,其基带噪声并不能降到低于10比特A/D转换器所要求的60dB的SNR要求。因此,要想尽量减少基带内的量化噪声,只有增加采样频率。但是,采样频率的增加受到电路工作频率和数字滤波器性能的制约。据此,为了增加噪声整形效果以便降低所需的采样频率,在一阶Σ-Δ调制器的基础上发展了各种各样的高阶Σ-Δ调制器。

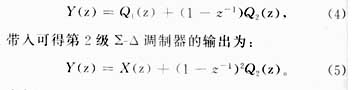

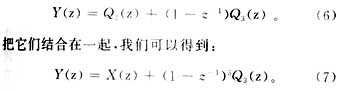

下面,我们先讨论二阶Σ-Δ调制器。既然这些层叠结构使用噪声前馈的方案,因此,系统总是稳定的。当多级一阶Σ-Δ回路叠用以获得高阶调制器时,传向后续回路的信号是当前回路的噪声。这个噪声是积分器输出与量化器输出的差值。

如果输入到第2和第3级Σ-Δ回路的信号分别是Q1,Q2,则第2级Σ-Δ调制器的量化输出为:

类似地,对于3阶ΣΔ调制器,

这里,Q3是第3级Σ-Δ调制器的量化噪声。

分析表明,3阶Σ-Δ调制器的带内量化噪声明显比1阶的小。

我们用Matlab语言对低通Σ-Δ A/D转换过程进行了仿真,得到的结果与理论分析十分相符(3阶环,输出SINAD约为108dB)。其主要程序略。

4 结束语

上面, 我们对低通Σ-Δ A/D转换技术作了较为详细的分析。国外从八十年代后期开始大规模地对Σ-Δ A/D和Σ-Δ D/A转换技术展开研究,目前,已有成熟的Σ-Δ ADC和Σ-ΔDAC产品。

参考文献

1 杨小牛等编著.软件无线电原理与应用.北京:电子工业出版社,2001

2 钮心忻等编著.软件无线电技术与应用.北京:北京邮电大学出版社,2001

粤公网安备 44030902003195号

粤公网安备 44030902003195号