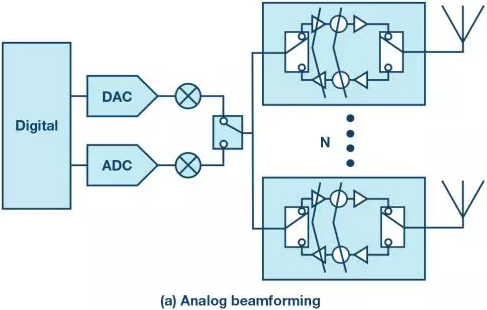

之前,我们分享了毫米波通信部署情形和传播注意事项,今天,我们来看一下各种波束合成方法:模拟、数字和混合,如图1所示。相信大家都很熟悉模拟波束合成的概念啦~

图1. 各种波束合成方法

在这里,我们有数据转换器,将数字信号与宽带基带或IF信号相互转换,连接执行上变频和下变频处理的无线电收发器。在射频(例如,28 GHz)中,我们将单个射频路径分成多条路径,通过控制每个路径的相位来执行波束合成,从而在远场朝目标用户的方向形成波束。这使得每条数据路径都能引导单个波束,因此理论上来说,我们可以使用该架构一次为一个用户服务。

数字波束成型就是字面意思。相移完全在数字电路中实现,然后通过收发器阵列馈送到天线阵列。简单地说,每个无线电收发器都连接到一个天线元件,但实际上每个无线电都可以有多个天线元件,具体取决于所需扇区的形状。该数字方法可实现最大容量和灵活性,并支持毫米波频率的多用户MIMO发展规划,类似于中频系统。这非常复杂,考虑到目前可用的技术,无论是在射频还是数字电路中,都将消耗过多的直流电。然而,随着未来技术的发展,毫米波无线电将出现数字波束合成。

近期最实用、最有效的波束合成方法是混合数模波束成型,它实质上是将数字预编码和模拟波束合成结合起来,在一个空间(空间复用)中同时产生多个波束。通过将功率引导至具有窄波束的目标用户,基站可以重用相同的频谱,同时在给定的时隙中为多个用户服务。虽然文献中报道的混合波束成型有几种不同的方法,但这里显示的子阵方法是最实际的实现方法,本质上是模拟波束成型的步骤和重复。目前,报告的系统实际上支持2到8个数字流,可以用于同时支持单个用户,或者向较少数量的用户提供2层或更多层的MIMO。

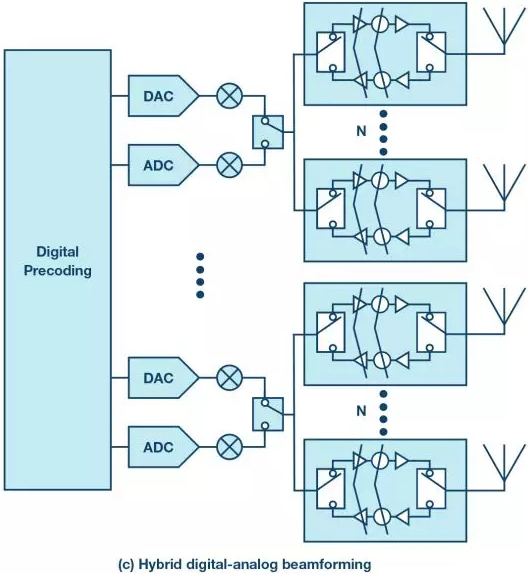

让我们更深入地探讨模拟波束成型的技术选择,即构建混合波束成型的构建模块,如图2所示。在这里,我们将模拟波束合成系统分为三个模块进行处理:数字、位到毫米波和波束成型。这并非实际系统的划分方式,因为人们会把所有毫米波组件放在邻近位置以减少损耗,但是这种划分的原因很快就会变得很明显。

图2. 模拟波束合成系统方框图

波束成型功能受到许多因素的推动,包括分段形状和距离、功率电平、路径损耗、热限制等,是毫米波系统的区段,随着行业的学习和成熟,需要一定的灵活性。即便如此,仍将继续需要各种传输功率电平,以解决从小型蜂窝到宏的不同部署情形。另一方面,用于基站的位到毫米波无线电需要的灵活性则要小得多,并且在很大程度上可以从当前Release 15规格中派生出来。换言之,设计人员可以结合多个波束成型配置重用相同的无线电。这与当前的蜂窝无线电系统没有什么不同,在这些系统中,小信号段跨平台很常见,而且每个用例的前端更多都是定制的。

当我们从数字转向天线时,就已经为信号链绘制了潜在技术的进展图。当然,数字信号和混合信号都是在细线体CMOS工艺中产生的。根据基站的要求,整个信号链可以用CMOS开发,或者更有可能的是,采用多种技术的混合开发,为信号链提供最佳性能。例如,一种常见的配置是使用具有高性能SiGe BiCMOS IF 到毫米波转换的CMOS数据转换器。如图所示,波束成型可采用多种技术实现,具体取决于系统需求,我们将在下面讨论。根据所选的天线尺寸和发射功率要求,可以实现高度集成的硅方法,也可以是硅波束成型与离散PA和LNA的组合。

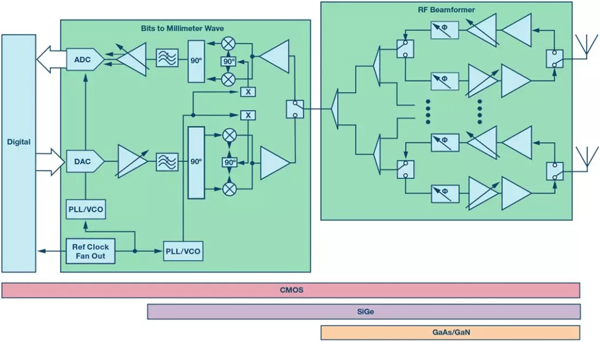

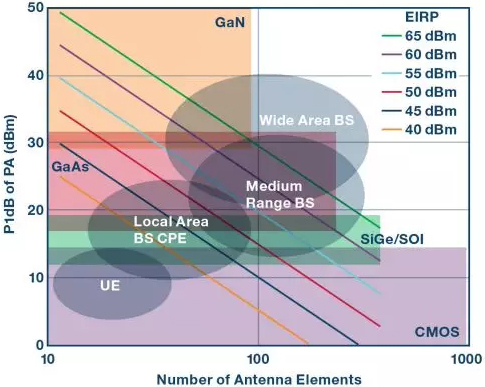

在之前的工作中,对变送器功率与技术选择之间的关系进行了分析,在此不再全面重复。但是,为了总结这一分析,我们在图3中包含了一个图表。功率放大器技术的选择基于综合考虑所需的变送器功率、天线增益(元件数)和所选技术的RF发电能力。

图3. 60 dBm EIRP的天线所需的变送器功率、天线尺寸和半导体技术选择之间的关系

如图所示,可以在前端使用II-V技术(低集成方法)或使用基于硅的高集成方法,通过较少的天线元件来实现所需的EIRP。每种方法都有各自的优缺点,而实际的实现取决于工程在规模、重量、直流功耗和成本方面的权衡。为了为表1中导出的案例生成60 dBm的EIRP,ADI 公司Thomas Cameron 博士在2018 国际固态电路会议上的演示文稿“5G毫米波无线电的架构与技术”中进行的分析得出,最佳天线尺寸介于128至256个元件之间,较低的数量通过GaAs功率放大器实现,而较大的数量可 采用全硅波束成型基于RF IC的技术实现。

表1. 5G基站示例

现在让我们从不同的角度来研究这个问题。60 dBm EIRP是FWA常用的EIRP目标,但数值可能更高或更低,具体取决于基站和周围环境的期望范围。由于部署情形变化很大,无论是树木成荫的地区、街道峡谷地区,还是广阔的空地,都有大量的路径损耗需要根据具体情况进行处理。例如,在假定为LOS的密集城市部署中,EIRP目标可能低至50 dBm。

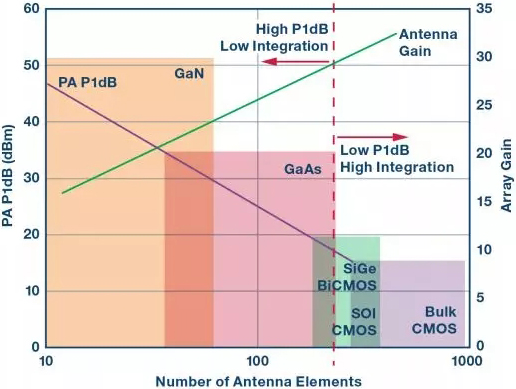

FCC按设备类别设定有定义和发布的规格,以及发射功率限制,这里我们遵循基站的3GPP术语。如图4所示,设备类别或多或少地限定了功率放大器的技术选择。

图4. 基于变送器功率的各种毫米波无线电尺寸适配技术

虽然这不是一门精确的科学,但我们可以看到,移动用户设备(手机)非常适合CMOS技术,相对较低的天线数量可以达到所需的变送器功率。这种类型的无线电将需要高度集成和省电才能满足便携式设备的需求。本地基站(小型蜂窝)和消费者终端设备(可移动电 源)要求类似,涉及从变送器功率要求低端的CMOS到更高端的SiGe BiCMOS的一系列技术。中程基站非常适合SiGe BiCMOS技 术,可实现紧凑的外形尺寸。在高端,对于广域基站来说,可以应用各种技术,具体取决于对天线尺寸和技术成本的权衡。尽管可在60 dBm EIRP范围内应用SiGe BiCMOS,但GaAs或GaN功率放大器更适合更高的功率。

图4显示了当前技术的快照,但行业正在取得很大进展,技术也在不断改进,而提高毫米波功率放大器的直流功率效率是设计人员面临的主要挑战之一。

随着新技术和PA架构的出现,上面的曲线将发生变化,并将为高功率基站提供集成度更高的结构。最后我们再复习一下上面的观点,对波束成型部分进行总结——目前还没有一种万能的方法,可能需要设计各种前端设计来解决从小型蜂窝到宏的各种用例。

粤公网安备 44030902003195号

粤公网安备 44030902003195号