з”ЁдәҺRF收еҸ‘еҷЁзҡ„з®ҖеҚ•еҹәеёҰеӨ„зҗҶеҷЁ

з®Җд»Ӣ

еҰӮд»ҠпјҢж— зәҝзі»з»ҹж— еӨ„дёҚеңЁпјҢж— зәҝи®ҫеӨҮе’ҢжңҚеҠЎзҡ„ж•°йҮҸжҢҒз»ӯеўһй•ҝгҖӮи®ҫи®Ўе®Ңж•ҙзҡ„RFзі»з»ҹжҳҜдёҖйЎ№и·ЁеӯҰ科и®ҫи®ЎжҢ‘жҲҳпјҢжЁЎжӢҹRFеүҚз«ҜжҳҜе…¶дёӯжңҖе…ій”®зҡ„йғЁеҲҶгҖӮ然иҖҢпјҢAD9361зӯүйӣҶжҲҗRF收еҸ‘еҷЁзҡ„жҺЁеҮәжҳҫи‘—еҮҸе°‘дәҶжӯӨзұ»и®ҫи®Ўзҡ„RFжҢ‘жҲҳгҖӮиҝҷдәӣ收еҸ‘еҷЁеҸҜдёәжЁЎжӢҹRFдҝЎеҸ·й“ҫжҸҗдҫӣж•°еӯ—жҺҘеҸЈпјҢе…Ғи®ёиҪ»жқҫйӣҶжҲҗеҲ°ASICжҲ–FPGAпјҢиҝӣиЎҢеҹәеёҰеӨ„зҗҶгҖӮеҹәеёҰеӨ„зҗҶеҷЁ(BBP)е…Ғи®ёеңЁз»Ҳз«Ҝеә”з”Ёе’Ң收еҸ‘еҷЁи®ҫеӨҮд№Ӣй—ҙзҡ„ж•°еӯ—еҹҹдёӯеӨ„зҗҶз”ЁжҲ·ж•°жҚ®гҖӮжӯӨеӨ–пјҢдҪҝз”ЁSimulinkзӯүзі»з»ҹе»әжЁЎе·Ҙе…·еҸҜд»ҘиҪ»жқҫе®ҢжҲҗеҹәеёҰеӨ„зҗҶеҷЁи®ҫи®ЎгҖӮ然иҖҢпјҢж–°жүӢз”ЁжҲ·еҸҜиғҪдјҡеҸ‘зҺ°йҡҫд»ҘзҗҶи§Је’Ңи§ЈеҶіиҝҷдёӘйҖҡдҝЎзі»з»ҹйҡҫйўҳгҖӮжң¬ж–Үе°қиҜ•дёәж— зәҝдј иҫ“йҖҡдҝЎзі»з»ҹи®ҫи®Ўе’Ңе®һж–Ҫз®ҖеҚ•зҡ„RFеҹәеёҰеӨ„зҗҶеҷЁгҖӮи®ҫи®ЎдҪҝз”ЁAD9361 FPGAеҸӮиҖғи®ҫи®ЎжЎҶжһ¶пјҢеңЁAD-FMCOMMS2-EBZе’ҢXilinx® ZC706е№іеҸ°дёҠе®һж–ҪгҖӮ

жң¬ж–Ү第дёҖйғЁеҲҶиҜҰз»ҶжҸҸиҝ°иҜҘеҹәеёҰеӨ„зҗҶеҷЁзҡ„дёҖиҲ¬и®ҫи®ЎеҺҹеҲҷгҖӮиҜҘйғЁеҲҶдё»иҰҒжҳҜBBPзҡ„зҗҶи®әд»Ӣз»ҚгҖӮеңЁз¬¬дәҢйғЁеҲҶпјҢдҪҝз”ЁADIе…¬еҸёзҡ„AD9361FPGAеҸӮиҖғи®ҫи®Ўи®Ёи®әBBPзҡ„е®һйҷ…硬件е®һж–ҪгҖӮеҖјеҫ—жіЁж„Ҹзҡ„жҳҜпјҢдё»иҰҒи®ҫи®Ўзӣ®ж ҮжҳҜдҪҝи®ҫи®Ўе°ҪеҸҜиғҪз®ҖеҚ•пјҢ并еңЁе®һйӘҢе®ӨзҺҜеўғдёӯжј”зӨәеҝ«йҖҹж— зәҝж•°жҚ®дј иҫ“гҖӮеңЁдҪҝз”Ёе’Ңе№Іжү°RFйў‘и°ұж—¶пјҢйЎ»иҖғиҷ‘еҲ°жі•и§„еҸҠе…¶д»–еҪұе“ҚгҖӮ

еҹәжң¬и®ҫи®Ў

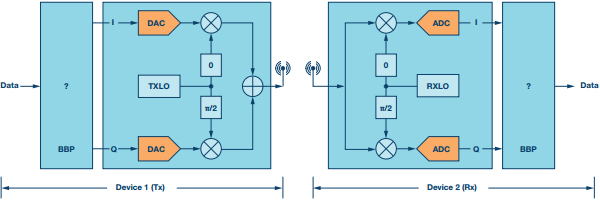

е…ёеһӢзҡ„RFзі»з»ҹеҰӮеӣҫ1жүҖзӨәпјҢзӣҙжҺҘRFзі»з»ҹйҷӨеӨ–гҖӮиҜҘеӣҫ1д»…жҳҫзӨәдәҶеҚ•дёӘж•°жҚ®и·Ҝеҫ„пјҢеҸҚж–№еҗ‘жҳҜиҜҘж•°жҚ®и·Ҝеҫ„зҡ„й•ңеғҸеӣҫеғҸгҖӮжң¬ж–ҮдёӯжҸҗеҮәзҡ„зӣёе…іеҹәеёҰеӨ„зҗҶеҷЁе…Ғи®ёеҜ№ж•°жҚ®иҝӣиЎҢеӨ„зҗҶпјҢд»ҘдҪҝе…¶еңЁдёӨдёӘRFзі»з»ҹд№Ӣй—ҙиҝӣиЎҢж— зәҝдј иҫ“гҖӮдёӢж–Үи®Ёи®әдәҶеҹәжң¬и®ҫи®ЎиҰҒжұӮгҖӮ

еӣҫ1. RFзі»з»ҹжЎҶеӣҫ

еңЁдёӨдёӘжӯЈдәӨдҝЎеҸ·I&QдёҠйҮҚеӨҚж•°жҚ®

жіЁж„ҸпјҢиҪҪжіўзӣёдә’зӢ¬з«Ӣдё”еҪјжӯӨдёҚеҗҢжӯҘгҖӮеӣ жӯӨпјҢеҸ‘е°„е’ҢжҺҘ收иҪҪжіўд№Ӣй—ҙеӯҳеңЁзӣёдҪҚе’Ңйў‘зҺҮеҒҸ移гҖӮиҝҷе°ҶеҜ№жҺҘ收еҷЁзҡ„и§Ји°ғдә§з”ҹдёҚеҲ©еҪұе“ҚгҖӮдёҖдёӘйҮҚиҰҒй—®йўҳжҳҜдҝЎеҸ·еҸҚиҪ¬пјҢжӯЈдәӨдҝЎеҸ·еҸҜиғҪдјҡеҸҚиҪ¬е…¶дҪңз”ЁпјҢеӣ дёәеҒҸ移дјҡе®ҡжңҹеҗҲ并е’ҢжјӮзҰ»гҖӮе…ӢжңҚиҝҷз§ҚдёҚзЎ®е®ҡжҖ§зҡ„з®ҖеҚ•ж–№жі•жҳҜеңЁдёӨдёӘжӯЈдәӨдҝЎеҸ·дёҠйҮҚеӨҚзӣёеҗҢж•°жҚ®гҖӮ

д»ҘдёІиЎҢеҪўејҸеҸ‘йҖҒе’ҢжҺҘ收数жҚ®(жҢүдҪҚ)

еӨ§еӨҡж•°жғ…еҶөдёӢпјҢдёҺBBPиҝһжҺҘзҡ„RFеүҚз«ҜжҺҘеҸЈжҳҜDACе’ҢADCгҖӮиҝҷдәӣжҳҜжЁЎжӢҹдҝЎеҸ·зҡ„ж•°еӯ—жҺҘеҸЈгҖӮеӣ жӯӨпјҢдёҚиғҪз®ҖеҚ•ең°е°Ҷж•°жҚ®еҸ‘йҖҒеҲ°DACиҫ“е…ҘпјҢ并预计еңЁADCиҫ“еҮәз«ҜиҺ·еҫ—зӣёеҗҢж•°жҚ®гҖӮж•°жҚ®д»ҘдёІиЎҢеҪўејҸеҸ‘е°„пјҢе°ҶеҚ•дёӘдҪҚж•°жҚ®жҳ е°„еҲ°DACзҡ„е…ЁйғЁеҲҶиҫЁзҺҮгҖӮеҗҢж ·пјҢж•°жҚ®д»ҘдёІиЎҢеҪўејҸжҺҘ收пјҢд»ҺADCзҡ„е…ЁйғЁеҲҶиҫЁзҺҮи§Јжҳ е°„гҖӮиҝҷжҸҗдҫӣдәҶе……и¶ізҡ„еҶ—дҪҷгҖӮеҰӮжһңиҝҷдәӣжҳҜ16дҪҚиҪ¬жҚўеҷЁпјҢеҲҷжҺҘ收еҷЁе°Ҷд»ҺеҸҜиғҪзҡ„65536ж•°жҚ®йӣҶдёӯеҶіе®ҡ1жҲ–0гҖӮд»…иҝҷдёҖзӮ№пјҢдҫҝеҸҜд»Ҙжҳҫи‘—з®ҖеҢ–и§Јз ҒгҖӮ

I&QдҝЎеҸ·зӣёдә’жӯЈдәӨ

RFеүҚз«Ҝи®ҫеӨҮ(еҰӮAD9361)жҳҜI/Q收еҸ‘еҷЁгҖӮеҰӮжһңиҫ“е…ҘжҳҜжӯЈдәӨдҝЎеҸ·пјҢиҝҷдәӣи®ҫеӨҮжңҖжңүж•ҲгҖӮиҝҷдәӣи®ҫеӨҮйҖҡеёёжІҝдёӨдёӘж•°жҚ®и·Ҝеҫ„иҝӣиЎҢеҶ…йғЁI/QеҢ№й…Қе’Ңж ЎжӯЈпјҢд»ҘжҠөж¶ҲдәҢиҖ…д№Ӣй—ҙзҡ„д»»дҪ•е·®ејӮгҖӮ规еҲҷжҳҜпјҢе®һйғЁ(I)дҝЎеҸ·жҳҜдҪҷејҰеҮҪж•°пјҢиҷҡйғЁ(Q)дҝЎеҸ·жҳҜжӯЈејҰеҮҪж•°гҖӮ

и°ғеҲ¶ж–№жЎҲжҳҜBPSK

еҸҜд»ҘйғЁзҪІдҝЎеҸ·е№…еәҰгҖҒйў‘зҺҮжҲ–зӣёдҪҚи°ғеҲ¶зҡ„жүҖжңүеёёи§Ғж–№жі•гҖӮжЈҖжөӢзӣёдҪҚе·®ејӮзӣёеҜ№жқҘиҜҙжӣҙеҠ з®ҖеҚ•гҖӮз”ұдәҺж•°жҚ®д»ҘдёІиЎҢеҪўејҸдј иҫ“пјҢеӣ жӯӨеҝ…然дјҡйҖүжӢ©дәҢиҝӣеҲ¶зӣёз§»й”®жҺ§(BPSK)гҖӮ

дҪҚй—ҙйҡ”жҳҜ8дёӘж ·жң¬

ж•°жҚ®йңҖиҰҒж—¶еәҸдҝЎжҒҜпјҢдҪҚй—ҙйҡ”гҖӮеҸҜиғҪзҡ„жңҖеӨ§дҪҚй—ҙйҡ”жҳҜйҮҮж ·е‘ЁжңҹгҖӮдёәдәҶдҪҝжҺҘ收еҷЁдҝқжҢҒз®ҖеҚ•пјҢйңҖиҰҒи¶іеӨҹзҡ„ж—¶й—ҙжқҘи§Јз ҒдҝЎеҸ·е№¶еҒҡеҮәеҶіе®ҡгҖӮжңҖз®ҖеҚ•зҡ„ж—¶еәҸжҒўеӨҚж–№жі•жҳҜйӣ¶дәӨи¶Ҡе’Ңеі°еҖјжЈҖжөӢгҖӮеңЁиҝҷз§Қжғ…еҶөдёӢпјҢеі°еҖје°ҶдёҚдёҖиҮҙгҖӮеӣ жӯӨпјҢйҖүжӢ©йӣ¶дәӨи¶ҠиҝӣиЎҢдҪҚй—ҙйҡ”жЈҖжөӢе’Ңи·ҹиёӘгҖӮдёӨз§Қзі»з»ҹд№Ӣй—ҙд№ҹеӯҳеңЁиҪҪжіўе·®ејӮгҖӮеңЁжҹҗдәӣжғ…еҶөдёӢпјҢеңЁз”ЁжҲ·ж•°жҚ®зҡ„д»»ж„Ҹз«ҜпјҢж ·жң¬еҸҜиғҪжЁЎзіҠдёҚжё…гҖӮдёәжҜҸеҚҠдёӘжӯЈејҰдҝЎеҸ·з•ҷеҮә4дёӘж ·жң¬пјҢдҪҚй—ҙйҡ”и®ҫзҪ®дёә8дёӘж ·жң¬гҖӮеӣ жӯӨпјҢжңүж•Ҳзҡ„дј иҫ“йҖҹзҺҮжҳҜйҮҮж ·йў‘зҺҮйҷӨд»Ҙ8гҖӮ

ж•°жҚ®жІЎжңүзӣҙжөҒжҲҗеҲҶ

ж—¶еәҸе’ҢзӣёеҜ№зӣёдҪҚжҒўеӨҚд»ҘдҝЎеҸ·зҡ„йӣ¶дәӨи¶ҠдёәеҹәзЎҖгҖӮеӣ жӯӨпјҢеҚ•дёӘдҝЎеҸ·йңҖиҰҒдёҚеҗ«д»»дҪ•зӣҙжөҒжҲҗеҲҶгҖӮжӯӨеӨ–пјҢиҰҒжұӮдҝЎеҸ·жҜҸйҡ”дёҖдёӘдҪҚй—ҙйҡ”е…Ғи®ёиҮіе°‘дёҖдёӘйӣ¶дәӨи¶ҠгҖӮжӯЈејҰдҝЎеҸ·е…је…·дёӨиҖ…зҡ„еұһжҖ§пјҢ并且йқһеёёз¬ҰеҗҲдёҠиҝ°BPSKи°ғеҲ¶ж–№жЎҲиҰҒжұӮгҖӮ

ж•°жҚ®е·ІеҠ жү°

з”ЁжҲ·ж•°жҚ®жҳҜд»»ж„Ҹзҡ„еҫҲеҸҜиғҪжҳҜдёҖй•ҝдёІ1жҲ–0гҖӮж•°жҚ®йңҖиҰҒеҠ жү°пјҢд»ҘдҫҝеңЁжҺҘ收еҷЁз«ҜжҒўеӨҚж—¶еәҸе’ҢзӣёдҪҚпјҢд»ҺиҖҢжӣҙй«ҳж•Ҳең°и·ҹиёӘдҝЎеҸ·гҖӮ

ж•°жҚ®д»Ҙж•°жҚ®еҢ…зҡ„еҪўејҸдј иҫ“

з”ұдәҺзі»з»ҹеҪјжӯӨдёҚеҗҢжӯҘпјҢеӣ жӯӨжҺҘ收еҷЁзҡ„дҝЎеҸ·дјҡеӯҳеңЁе№…еәҰгҖҒйў‘зҺҮе’ҢзӣёдҪҚиҜҜе·®гҖӮи§Ји°ғдҝЎеҸ·жҳҜеҸ‘е°„дҝЎеҸ·зӣёеҜ№дәҺжң¬ең°иҪҪжіўеҸ‘з”ҹзӣёдҪҚеҸҳеҢ–зҡ„дҝЎеҸ·гҖӮиҪҪжіўеҸҜиғҪдјҡи·ҹиёӘдёҖж®өж—¶й—ҙпјҢйҖүеҸ–ж•°жҚ®пјҢ然еҗҺеҶҚи·ҹиёӘгҖӮеӣ жӯӨпјҢи®ҫи®ЎйңҖиҰҒеҒҡеҘҪйғЁеҲҶж•°жҚ®дёўеӨұзҡ„еҮҶеӨҮгҖӮдёәжӯӨпјҢж•°жҚ®д»Ҙж•°жҚ®еҢ…зҡ„еҪўејҸдј иҫ“гҖӮеҸҜйҮҚеӨҚдј иҫ“еӨҡдёӘж•°жҚ®еҢ…пјҢиҖҢйқһж•ҙдёӘж•°жҚ®гҖӮ

дҪҝз”ЁCRCйӘҢиҜҒж•°жҚ®еҢ…

ж•°жҚ®еҢ…жҗәеёҰеҫӘзҺҜеҶ—дҪҷж ЎйӘҢ(CRC)з ҒпјҢеӣ жӯӨеҰӮжһңеӯҳеңЁдёҚеҢ№й…ҚпјҢеҲҷе…Ғи®ёжҺҘ收еҷЁдёўеҢ…пјҢ并иҜ·жұӮеҶҚж¬ЎеҸ‘йҖҒгҖӮ

еңЁжҜҸдёӘеүҚеҗҢжӯҘз Ғжңҹй—ҙе®ҢжҲҗж—¶еәҸе’ҢзӣёдҪҚж ЎжӯЈ

ж•°жҚ®еҢ…иЎЁеӨҙжҗәеёҰеүҚеҗҢжӯҘз ҒпјҢз”ЁдәҺе°Ҷе…¶д»ҺжҺҘ收еҲ°зҡ„ж•°жҚ®жөҒдёӯеҲ’еҲҶеҮәжқҘгҖӮжӯӨеӨ–пјҢжҺҘ收еҷЁдҪҝз”ЁиҜҘеүҚеҗҢжӯҘз ҒеӨҚдҪҚдҝЎеҸ·зҡ„ж—¶еәҸе’ҢзӣёдҪҚдҝЎжҒҜпјҢд»Ҙи§Ји°ғж•°жҚ®еҢ…ж•°жҚ®гҖӮ

еҶ…зҪ®жҖ§иғҪжҢҮж Ү

жҺҘ收еҷЁд№ҹж”ҜжҢҒз»ҹи®Ўи®Ўж•°еҷЁпјҢеҰӮжҺҘ收еҲ°зҡ„гҖҒдёўејғзҡ„жҲ–ж ЎжӯЈзҡ„ж•°жҚ®еҢ…ж•°йҮҸгҖӮиҝҷдәӣи®Ўж•°еҷЁз”ЁдәҺиЎЎйҮҸе’Ңзӣ‘жҺ§жҖ§иғҪжҢҮж ҮпјҢеҢ…жӢ¬иҜҜз ҒзҺҮе’Ңжңүж•Ҳж•°жҚ®йҖҹзҺҮгҖӮ

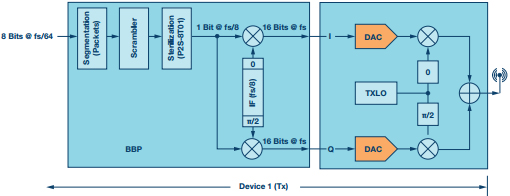

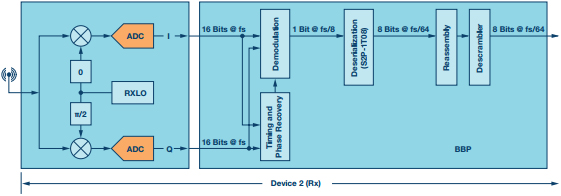

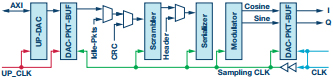

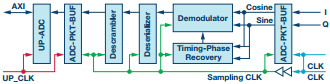

жҖ»иҖҢиЁҖд№ӢпјҢж•°жҚ®дҪңдёәж•°жҚ®еҢ…д»ҘдёІиЎҢеҪўејҸеҸ‘йҖҒе’ҢжҺҘ收гҖӮж•°жҚ®еҢ…жҗәеёҰеүҚеҗҢжӯҘз Ғе’ҢCRCгҖӮж•°жҚ®еңЁж”¶еҸ‘еҷЁи®ҫеӨҮеүҚзҡ„дёӯй—ҙжӯЈдәӨдҝЎеҸ·дёҠз»ҸиҝҮBPSKи°ғеҲ¶е’Ңи§Ји°ғгҖӮеӣ жӯӨпјҢдёӯй—ҙдҝЎеҸ·йў‘зҺҮе’Ңж•°жҚ®зҡ„дҪҚйҖҹзҺҮжҳҜйҮҮж ·йҖҹзҺҮзҡ„е…«еҲҶд№ӢдёҖгҖӮеҹәеёҰеӨ„зҗҶеҷЁжЁЎеқ—еҸҠдёҠиҝ°и®ҫи®Ўз»ҶиҠӮеҰӮеӣҫ2е’Ң3жүҖзӨәгҖӮ

еӣҫ2. BBPеҸ‘йҖҒеҠҹиғҪжЎҶеӣҫ

еӣҫ3. BBPжҺҘ收еҠҹиғҪжЎҶеӣҫ

еҸ‘йҖҒеҷЁиҜ»еҸ–ж•°жҚ®еӯ—иҠӮ(еӯ—з¬Ұе®ҪеәҰ)пјҢ并е°Ҷе…¶иҪ¬жҚўдёәеёҰжңүиЎЁеӨҙжҲ–еүҚеҗҢжӯҘз Ғзҡ„ж•°жҚ®еҢ…гҖӮе°ҶCRCж·»еҠ еҲ°ж•°жҚ®еҢ…жң«з«ҜгҖӮ然еҗҺпјҢеҜ№ж•°жҚ®еҢ…ж•°жҚ®иҝӣиЎҢеҠ жү°е’ҢдёІиЎҢеӨ„зҗҶгҖӮеңЁиҝһжҺҘеҲ°ж”¶еҸ‘еҷЁд№ӢеүҚпјҢеҚ•дёӘдҪҚж•°жҚ®зӣёдҪҚи°ғеҲ¶дҪҷејҰ(I)е’ҢжӯЈејҰ(Q)еҮҪж•°гҖӮ

еңЁжҺҘ收方еҗ‘пјҢзҰ»зәҝжЁЎеқ—жҒўеӨҚ并и·ҹиёӘж—¶еәҸй—ҙйҡ”е’Ңи°ғеҲ¶дҝЎеҸ·зҡ„зӣёеҜ№зӣёдҪҚгҖӮиҜҘдҝЎжҒҜз”ЁдәҺд»Һиҫ“е…Ҙзҡ„ADCж ·жң¬дёӯжҒўеӨҚдёІиЎҢж•°жҚ®гҖӮ然еҗҺз»„иЈ…еҲ°ж•°жҚ®еҢ…пјҢ并иҝӣиЎҢи§Јжү°гҖӮеңЁж•°жҚ®еҢ…з»“жқҹж—¶пјҢжҜ”иҫғCRCпјҢеҰӮжһңдёҚеҢ№й…ҚпјҢеҲҷдёўејғж•°жҚ®еҢ…гҖӮеҰӮжһңCRCеҢ№й…ҚпјҢж•°жҚ®дј йҖ’з»ҷз»Ҳз«Ҝз”ЁжҲ·гҖӮ

е®һзҺ°

BBPи®ҫи®ЎеңЁзЎ¬д»¶дёӯе®һж–Ҫе’ҢжөӢиҜ•гҖӮ硬件жҳҜдёӨдёӘиҜ„дј°жқҝзҡ„з»„еҗҲпјҡе…·жңүZynq FPGAи®ҫеӨҮзҡ„Xilinx ZC706иҜ„дј°жқҝпјҢд»ҘеҸҠе…·жңүAD9361收еҸ‘еҷЁзҡ„AD-FMCOMMS3-EBZиҜ„дј°жқҝгҖӮADIжҸҗдҫӣж”ҜжҢҒиҜҘ硬件зҡ„е®Ңж•ҙеҸӮиҖғи®ҫи®ЎгҖӮиҜҘејҖжәҗи®ҫи®ЎеңЁдё»иҰҒе·Ҙе…·зүҲжң¬дёӯе…Қиҙ№жҸҗдҫӣпјҢеҸҜиҺ·еҫ—е®Ңе…Ёж”ҜжҢҒе’Ңжӣҙж–°гҖӮ硬件иҜҰз»ҶдҝЎжҒҜеҸӮи§ҒдёӢеҲ—URLпјҡ

ZC706AD-FMCOMMS3-EBZ

Zynq SOC

AD9361

ADI GitHubеә“

ZC706е’ҢAD-FMCOMMS3-EBZ HDLеҸӮиҖғи®ҫи®Ў

AXI AD9361 IP

ADIеҸӮиҖғи®ҫи®ЎжҳҜж”ҜжҢҒLinux®жЎҶжһ¶зҡ„еөҢе…ҘејҸзі»з»ҹгҖӮеҢ…еҗ«еӣҙз»•ARM®еӨ„зҗҶеҷЁзҡ„еҗ„з§ҚеӨ–и®ҫгҖӮAD9361и®ҫеӨҮиҝһжҺҘеҲ°axi_AD9361 IPеӨ–и®ҫгҖӮе®ғеңЁRFи®ҫеӨҮе’Ңзі»з»ҹеӯҳеӮЁеҷЁд№Ӣй—ҙдј иҫ“еҺҹе§ӢйҮҮж ·ж•°жҚ®гҖӮеӨ–и®ҫе’Ңи®ҫеӨҮйҖҡиҝҮLinuxеҶ…ж ёй©ұеҠЁзЁӢеәҸиҝӣиЎҢеҲқе§ӢеҢ–е’ҢжҺ§еҲ¶гҖӮBBPеҲҷдҪңдёәиҝһжҺҘеҲ°axi_AD9361зҡ„еҸҰдёҖдёӘIPеӨ–и®ҫгҖӮеҮәдәҺеҺҶеҸІеҺҹеӣ пјҢBBP IPе‘ҪеҗҚдёәaxi_xcomm2ipгҖӮLinuxдёӯзҡ„з”ЁжҲ·з©әй—ҙеә”з”ЁзЁӢеәҸз”ЁдәҺеңЁзі»з»ҹд№Ӣй—ҙжҺ§еҲ¶гҖҒеҸ‘йҖҒе’ҢжҺҘ收数жҚ®гҖӮ

еңЁADIеҸӮиҖғи®ҫи®ЎдёӯпјҢеңЁеҸ‘йҖҒж–№еҗ‘пјҢaxi_AD9361 IPиҝһжҺҘеҲ°и§ЈеҢ…жЁЎеқ—(util_upack)пјҢеңЁжҺҘ收方еҗ‘пјҢиҝһжҺҘеҲ°жү“еҢ…жЁЎеқ—(util_cpack)гҖӮеңЁеҸ‘йҖҒж–№еҗ‘пјҢBBPж•°жҚ®жҸ’е…Ҙи§ЈеҢ…жЁЎеқ—е’ҢAD9361еҶ…ж ёд№Ӣй—ҙгҖӮдёәдәҶдҪҝе…¶дёҚеҪұе“Қй»ҳи®Өж•°жҚ®и·Ҝеҫ„пјҢBBPж”ҜжҢҒеҸҜйҖүзҡ„ж•°жҚ®и·Ҝеҫ„еӨҡи·ҜеӨҚз”ЁеҷЁпјҢд»ҘйҖүжӢ©и§ЈеҢ…ж•°жҚ®жәҗжҲ–BBPж•°жҚ®жәҗгҖӮBBPе…Ғи®ёеҸӮиҖғи®ҫи®Ўж•°жҚ®и·Ҝеҫ„дҪңдёәй»ҳи®Өи·Ҝеҫ„пјҢ并仅еңЁеҗҜз”Ёж—¶йҖүжӢ©BBPж•°жҚ®жәҗгҖӮеңЁжҺҘ收方еҗ‘пјҢBBPд»…иҝһжҺҘеҲ°AD9361еҶ…ж ёгҖӮеҸӮиҖғи®ҫи®Ўж•°жҚ®и·Ҝеҫ„дёҚеҸ—еҪұе“ҚгҖӮиҝҷе…Ғи®ёжЎҶжһ¶дёҚеҸ—еҰЁзўҚең°еј•еҜје’Ңи®ҫзҪ®зі»з»ҹгҖӮеңЁзі»з»ҹи®ҫзҪ®еҗҺпјҢеҗҜз”ЁBBPпјҢеҸҜйҖҡиҝҮиҰҶзӣ–й»ҳи®Өж•°жҚ®и·Ҝеҫ„жқҘиҝӣиЎҢж•°жҚ®дј иҫ“гҖӮд»ҘADIеҸӮиҖғи®ҫи®Ўе®һж–Ҫзҡ„BBPзҡ„жЎҶеӣҫеҰӮеӣҫ4жүҖзӨәгҖӮ

еӣҫ4. BBP IPжЎҶеӣҫ

жң¬ж–Үдёӯи®Ёи®әзҡ„и®ҫи®ЎгҖҒеҲқе§ӢеҢ–е’Ңж•°жҚ®дј иҫ“дҪҝз”ЁдёҖеҜ№иҝҷз§Қ硬件гҖӮи®ҫзҪ®д»…йңҖдёҖеҜ№HDMI®зӣ‘и§ҶеҷЁгҖҒй”®зӣҳе’Ңйј ж ҮеҸҠеӨ©зәҝгҖӮзі»з»ҹеҪјжӯӨе®Ңе…ЁдёҚеҗҢжӯҘпјҢдҪҶйңҖиҰҒзӣёеҗҢи®ҫзҪ®гҖӮеңЁжҜҸдёӘж–№еҗ‘пјҢж•°жҚ®еңЁдёҚеҗҢиҪҪжіўдёҠдј иҫ“гҖӮи®ҫеӨҮ1зҡ„еҸ‘е°„иҪҪжіўйў‘зҺҮе’Ңи®ҫеӨҮ2зҡ„жҺҘ收иҪҪжіўйў‘зҺҮзӣёеҗҢпјҢдҪҶеңЁеҸҰдёҖдёӘж–№еҗ‘дёҠдёҚеҗҢгҖӮ然иҖҢпјҢеҰӮжһңеӣһйҖҒдёӯдҪҝз”ЁеҚ•дёӘи®ҫеӨҮпјҢеҸ‘е°„е’ҢжҺҘ收иҪҪжіўеҝ…йЎ»е…·жңүзӣёеҗҢзҡ„йў‘зҺҮгҖӮBBPзҡ„HDLи®ҫи®ЎйҮҮз”ЁADIеә“жЁЎеқ—гҖӮ

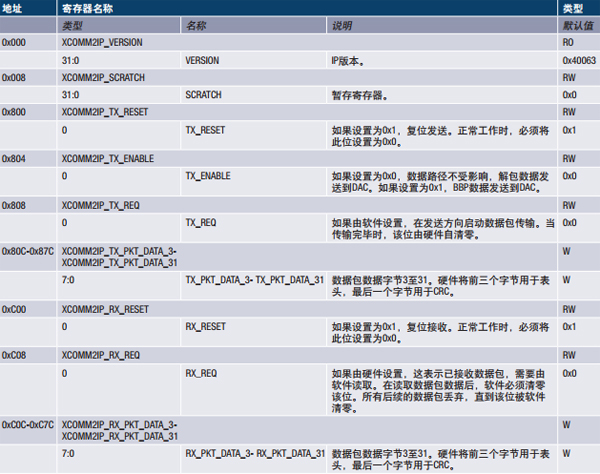

иЎЁ1. BBPеҜ„еӯҳеҷЁжҳ е°„

жҺ§еҲ¶(еҫ®еӨ„зҗҶеҷЁ)жҺҘеҸЈ

AXI-LiteжҺҘеҸЈз”ЁдәҺйҖҡиҝҮеӨ„зҗҶеҷЁжҺ§еҲ¶е’Ңзӣ‘жҺ§BBPгҖӮдҪҝз”ЁADIе…¬е…ұеә“(hdl/library/common/up_axi.v)дёӯзҡ„up_axiжЁЎеқ—пјҢеҸҜд»ҘиҪ»жқҫжҺЁж–ӯиҜҘжҺҘеҸЈжЁЎеқ—гҖӮиҜҘжЁЎеқ—е°ҶAXI-LiteжҺҘеҸЈиҪ¬жҚўдёәз®ҖеҚ•еҶ…еӯҳпјҢеҰӮиҜ»еҸ–е’ҢеҶҷе…ҘжҖ»зәҝгҖӮе’Ңд»»дҪ•е…¶д»–ADI IPдёҖж ·пјҢж·»еҠ еҶ…йғЁеҜ„еӯҳеҷЁе’ҢеҶ…еӯҳгҖӮеҜ„еӯҳеҷЁжҳ е°„еҰӮиЎЁ1жүҖзӨәгҖӮ

up_axiжЁЎеқ—з«ҜеҸЈеҸҠе…¶з«ҜеҸЈжҳ е°„еҰӮдёӢжүҖиҝ°гҖӮup_rstnпјҡAXIжҺҘеҸЈеӨҚдҪҚ(ејӮжӯҘдҪҺз”өе№іжңүж•Ҳ)пјҢиҝһжҺҘеҲ°s_axi_aresetnгҖӮ

up_clkпјҡAXIжҺҘеҸЈж—¶й’ҹпјҢиҝһжҺҘеҲ°s_axi_aclkгҖӮ

up_axi_*пјҡAXIжҺҘеҸЈдҝЎеҸ·пјҢиҝһжҺҘеҲ°зӯүж•Ҳs_axi_*з«ҜеҸЈгҖӮ

up_wreq, up_waddr, up_wdata, up_wackпјҡеҶ…йғЁеҶҷе…ҘжҺҘеҸЈпјҢup_wreqдҝЎеҸ·дёҺең°еқҖе’Ңж•°жҚ®дёҖеҗҢзҪ®дҪҚпјҢд»ҘжҢҮзӨәеҶҷе…ҘиҜ·жұӮгҖӮиҜ·жұӮйңҖиҰҒйҖҡиҝҮup_wackз«ҜеҸЈеә”зӯ”гҖӮ

еҰӮдёӢжүҖзӨәпјҢе®һж–Ҫз®ҖеҚ•зҡ„еҜ„еӯҳеҷЁеҶҷе…ҘгҖӮ

always @(negedge up_rstn or posedge up_clk)begin

if (up_rstn == 0) begin

up_wack up_reg0 end else begin

up_wack if ((up_wreq_s == 1’b1) && (up_waddr == UP_

REG0_ADDRESS)) begin

up_reg0 end

end

end

жЁЎеқ—еңЁдәҢиҖ…д№Ӣй—ҙжү§иЎҢең°еқҖиҪ¬жҚўгҖӮAXIжҺҘеҸЈдҪҝз”Ёеӯ—иҠӮең°еқҖпјҢдҪҶеҶ…йғЁжҖ»зәҝдҪҝз”ЁDWORDең°еқҖгҖӮз»“жһңжҳҜпјҢup_axiжЁЎеқ—дёўејғAXIең°еқҖзҡ„дёӨдёӘжңҖдҪҺжңүж•ҲдҪҚпјҢд»Ҙз”ҹжҲҗеҶ…йғЁDWORDең°еқҖгҖӮ

up_rreq, up_raddr, up_rdata, up_rackпјҡеҶ…йғЁиҜ»еҸ–жҺҘеҸЈпјҢup_rreqдҝЎеҸ·дёҺең°еқҖдёҖеҗҢзҪ®дҪҚпјҢд»ҘжҢҮзӨәиҜ»еҸ–иҜ·жұӮгҖӮиҜ·жұӮйңҖиҰҒдёҺиҜ»еҸ–ж•°жҚ®дёҖеҗҢйҖҡиҝҮup_rackз«ҜеҸЈеә”зӯ”гҖӮ

еҰӮдёӢжүҖзӨәпјҢе®һж–ҪдёҺдёҠиҝ°зӣёеҗҢзҡ„еҜ„еӯҳеҷЁз”ЁдәҺиҜ»еҸ–гҖӮ

always @(negedge up_rstn or posedge up_clk)begin

if (up_rstn == 0) begin

up_rack up_rdata end else begin

up_rack if ((up_rreq_s == 1’b1) && (up_raddr == UP_

REG0_ADDRESS)) begin

up_rdata end else begin

up_rdata end

end

end

зӣёеҗҢең°еқҖиҪ¬жҚўд№ҹйҖӮз”ЁдәҺиҜ»еҸ–гҖӮиҜ»еҸ–ж•°жҚ®д»…еңЁиҜ·жұӮж—¶й©ұеҠЁпјҢеҗҰеҲҷи®ҫзҪ®дёәйӣ¶гҖӮиҝҷжҳҜеӣ дёәup_axiжЁЎеқ—е°ҶеҚ•дёӘиҜ»еҸ–ж•°жҚ®д»Һеҗ„дёӘең°еқҖз»„дј йҖ’еҲ°ORй—ЁгҖӮеӣ жӯӨпјҢжңӘйҖүжӢ©зҡ„ең°еқҖз»„йңҖиҰҒй©ұеҠЁиҜ»еҸ–ж•°жҚ®йӣ¶гҖӮ

еҰӮдёҠж–№еҜ„еӯҳеҷЁжҳ е°„иЎЁдёӯжүҖеҲ—пјҢBBPжңүдёүдёӘең°еқҖз©әй—ҙгҖӮеёёи§ҒеҜ„еӯҳеҷЁз©әй—ҙжҳ е°„иҮі0x000гҖҒеҸ‘йҖҒ(DAC)жҳ е°„иҮі0x800 (0x200)пјҢжҺҘ收(ADC)жҳ е°„иҮі0xC00 (0x300)гҖӮиҪҜ件(Linuxз”ЁжҲ·з©әй—ҙеә”з”ЁзЁӢеәҸ)еә”еҪ“е°ҶеҸ‘йҖҒж•°жҚ®еҢ…ж•°жҚ®еҶҷе…Ҙзј“еҶІеҷЁпјҢ并д»ҺеҸҰдёҖдёӘзј“еҶІеҷЁдёӯиҜ»еҸ–жҺҘ收еҲ°зҡ„ж•°жҚ®еҢ…ж•°жҚ®гҖӮж•°жҚ®еҢ…еӨ§е°ҸйҖүжӢ©дёә32еӯ—иҠӮпјҢеёҰжңү3еӯ—иҠӮеүҚеҗҢжӯҘз Ғе’Ң1еӯ—иҠӮCRCгҖӮ

ж•°жҚ®жҺҘеҸЈ

еҜ№дәҺжҺҘ收е’ҢеҸ‘йҖҒж–№еҗ‘зҡ„дёӨдёӘйҖҡйҒ“пјҢAD9361жҺҘеҸЈеҶ…ж ёеҢ…еҗ«дёӨеҜ№16дҪҚI/Qж•°жҚ®гҖӮеҶ…ж ёжҢүз…§дёҺAD9361ж•°еӯ—жҺҘеҸЈзӣёеҗҢзҡ„ж—¶й’ҹиҝҗиЎҢгҖӮеңЁ2R2TжЁЎејҸдёӢпјҢиҝҷжҳҜйҮҮж ·йҖҹзҺҮзҡ„4еҖҚгҖӮеңЁ1R1TжЁЎејҸдёӢпјҢиҝҷжҳҜйҮҮж ·йҖҹзҺҮзҡ„2еҖҚгҖӮжңүж•Ҳж•°жҚ®йҖҹзҺҮз”ұжңүж•ҲдҝЎеҸ·жҺ§еҲ¶гҖӮеӣ жӯӨеңЁ2R2TжЁЎејҸдёӢпјҢжҜҸ4дёӘж—¶й’ҹзҪ®дҪҚдёҖж¬Ўжңүж•ҲгҖӮеңЁ1R1TжЁЎејҸдёӢпјҢжҜҸ2дёӘж—¶й’ҹзҪ®дҪҚдёҖж¬Ўжңүж•ҲгҖӮBBPж—ЁеңЁж”ҜжҢҒ2R2Tе’Ң1R1TжЁЎејҸгҖӮе®ғдҪҝз”ЁеҚ•дёӘеҸ‘йҖҒе’ҢжҺҘ收йҖҡйҒ“гҖӮеҶ…йғЁйҖ»иҫ‘еңЁ2R2Tе’Ң1R1TжЁЎејҸдёӢд»ҘйҮҮж ·йҖҹзҺҮиҝҗиЎҢгҖӮ然еҗҺпјҢBBPеңЁе…¶ж—¶й’ҹйў‘зҺҮдёӢпјҢйҖҡиҝҮжҺҘеҸЈеҶ…ж ёдј иҫ“ж•°жҚ®гҖӮиҝҷж ·жҳҜдёәдәҶеңЁBBPеҶ…жј”зӨәж—¶й’ҹиҪ¬жҚўгҖӮеңЁи®ёеӨҡжғ…еҶөдёӢпјҢз”ЁжҲ·еҸҜиғҪеёҢжңӣж— и®ә收еҸ‘еҷЁзҡ„жҺҘеҸЈйҖҹзҺҮеҰӮдҪ•пјҢйғҪиғҪеңЁйҮҮж ·йҖҹзҺҮдёӢиҝҗиЎҢBBPйҖ»иҫ‘гҖӮ

дҪҝз”ЁXilinxеҹәе…ғBUFRе’ҢBUFGпјҢз”ҹжҲҗйҮҮж ·йў‘зҺҮеҶ…йғЁж—¶й’ҹгҖӮBUFRжҳҜеҲҶеҺӢеҷЁпјҢBUFGжҳҜй«ҳжүҮеҮәж—¶й’ҹзј“еҶІеҷЁгҖӮдёәжӯӨпјҢд№ҹеҸҜд»ҘдҪҝз”ЁMMCMгҖӮеҰӮдёӢжүҖзӨәпјҢз”ҹжҲҗеҶ…йғЁж—¶й’ҹгҖӮ

parameter XCOMM2IP_1T1R_OR_2T2R_N = 0;localparam XCOMM2IP_SCLK_DIVIDE =

(XCOMM2IP_1T1R_OR_2T2R_N == 1) ? “2” : “4”;

BUFR #(.BUFR_DIVIDE(XCOMM2IP_SCLK_DIVIDE))

i_bufr (

.CLR (1’b0),

.CE (1’b1),

.I (clk),

.O (s_clk_s));

BUFG i_bufg (

.I (s_clk_s),

.O (s_clk));

дҪҝз”ЁBUFRе’ҢBUFGеҸҜзЎ®дҝқж—¶й’ҹйў‘зҺҮй”Ғе®ҡпјҢдҪҶдјҡеҪұе“ҚзӣёдҪҚзЎ®е®ҡжҖ§гҖӮжңҖеӨ§зӣёдҪҚдёҚзЎ®е®ҡжҖ§жҳҜеҚ•дёӘжҺҘеҸЈж—¶й’ҹе‘ЁжңҹгҖӮйҖҡиҝҮеёҰжңүеҗҢжӯҘдҝЎеҸ·зҡ„еӣӣзә§еҜ„еӯҳеҷЁйҳөеҲ—пјҢеҸҜд»ҘиҪ»жқҫиЎҘеҒҝиҜҘдёҚзЎ®е®ҡжҖ§гҖӮ然иҖҢпјҢи®ҫи®ЎйҮҮз”ЁдәҶеҸҢз«ҜеҸЈRAMжЁЎеқ—жқҘе®һзҺ°ж•°жҚ®дј иҫ“гҖӮиҝҷд№ҹжҳҜдёәдәҶеұ•зӨәеёёи§ҒдҝЎеҸ·еӨ„зҗҶиҰҒжұӮзҡ„еә”з”Ёе®һдҫӢгҖӮдҪҝз”ЁADIеә“еҶ…еӯҳжЁЎеқ—(ad_mem)еҸҜд»ҘжҺЁж–ӯеҮәеҸҢз«ҜеҸЈRAMе…ғ件гҖӮ

еҸ‘йҖҒжҺҘеҸЈ

еңЁеҸ‘йҖҒж–№еҗ‘пјҢеӨ„зҗҶеҷЁе°Ҷж•°жҚ®еҢ…ж•°жҚ®еҶҷе…Ҙзј“еҶІеҷЁ(еҸӮи§ҒдёҠж–№еҜ„еӯҳеҷЁжҳ е°„иЎЁ)гҖӮ然еҗҺпјҢиҜ·жұӮ硬件еҸ‘йҖҒиҜҘж•°жҚ®еҢ…гҖӮBBPе°Ҷж•°жҚ®еҢ…иҝһз»ӯеҸ‘йҖҒз»ҷи®ҫеӨҮгҖӮеңЁж•°жҚ®еҢ…ејҖе§Ӣж—¶пјҢжЈҖжҹҘжҳҜеҗҰжңүд»»дҪ•иҜ·жұӮгҖӮеҰӮжһңжІЎжңүеҫ…еӨ„зҗҶзҡ„иҜ·жұӮпјҢеҲҷеҸ‘йҖҒз©әй—Іж•°жҚ®еҢ…гҖӮеҰӮжһңжңүиҜ·жұӮзӯүеҫ…еӨ„зҗҶпјҢиҜ»еҸ–并еҸ‘йҖҒж•°жҚ®еҢ…зј“еҶІеҷЁгҖӮ

еҸ‘йҖҒйҖ»иҫ‘дҪҝз”ЁиҮӘз”ұиҝҗиЎҢдҪҚи®Ўж•°еҷЁпјҢжҢүз…§дҪҚе®ҪиҝҗиЎҢгҖӮеҪ“дҪҚи®Ўж•°еҷЁдёә0x0ж—¶пјҢжӣҙж–°зј“еҶІеҷЁиҜ»еҸ–ең°еқҖгҖӮз”ұдәҺеңЁж•°жҚ®еҢ…дј иҫ“жңҹй—ҙеҸҜиғҪдјҡйҡҸж—¶еҮәзҺ°еӨ„зҗҶеҷЁиҜ·жұӮпјҢеӣ жӯӨеңЁж•°жҚ®еҢ…дј иҫ“ејҖе§Ӣж—¶дјҡз«ӢеҚіжҚ•иҺ·е№¶жё…йӣ¶гҖӮеңЁж•°жҚ®еҢ…дј иҫ“ејҖе§Ӣж—¶пјҢеҰӮжһңиҜ·жұӮзӯүеҫ…еӨ„зҗҶпјҢеҲҷеә”зӯ”еӣһиҮіеӨ„зҗҶеҷЁжҺҘеҸЈгҖӮеҲ©з”ЁиҜ·жұӮеңЁзј“еҶІеҷЁж•°жҚ®жҲ–з©әй—Іж•°жҚ®д№Ӣй—ҙиҝӣиЎҢйҖүжӢ©гҖӮ

еӣҫ5. еҸ‘йҖҒж•°жҚ®и·Ҝеҫ„

ж•°жҚ®еҢ…ж•°жҚ®зҡ„еүҚдёӨдёӘеӯ—иҠӮи®ҫзҪ®дёә0xfff0гҖӮ第дёүдёӘеӯ—иҠӮз”ЁдәҺиЎЁзӨәз©әй—І(0xc5)жҲ–ж•°жҚ®(0xa6)ж•°жҚ®еҢ…гҖӮCRCеӯ—иҠӮдҪңдёәж•°жҚ®еҢ…зҡ„жңҖеҗҺдёҖдёӘеӯ—иҠӮжҸ’е…ҘгҖӮCRCеӨҡйЎ№ејҸдёәx8 + x2 + x + 1гҖӮйҷӨиЎЁеӨҙеӨ–зҡ„жүҖжңүеӯ—иҠӮе·ІеҠ жү°гҖӮеҠ жү°еӨҡйЎ№ејҸдёҺSONET/SDH (x7 + x6 + 1)зӣёеҗҢгҖӮ

дҪҷејҰе’ҢжӯЈејҰжҹҘжүҫиЎЁз”ЁдәҺз”ҹжҲҗи°ғеҲ¶иҪҪжіўгҖӮеңЁ8дёӘж ·жң¬дёӯпјҢдҪҚй—ҙйҡ”зӯүдәҺе®Ңж•ҙзҡ„дҝЎеҸ·е‘Ёжңҹ(0иҮі2)гҖӮдҪҚж•°жҚ®з”ЁдәҺеҸҚиҪ¬дҝЎеҸ·гҖӮ然еҗҺпјҢж•°жҚ®еҶҷе…Ҙе°Ҹзј“еҶІеҷЁпјҢ并дҪҝз”ЁжҺҘеҸЈж—¶й’ҹпјҢж №жҚ®AD9361жҺҘеҸЈеҶ…ж ёдёӯзҡ„жңүж•ҲдҝЎеҸ·иҜ»еҸ–гҖӮ

жҺҘ收жҺҘеҸЈ

еңЁжҺҘ收方еҗ‘пјҢй’ҲеҜ№иЎЁеӨҙжЁЎејҸ0xfff0пјҢзӣ‘жҺ§I/Qж•°жҚ®гҖӮиҝҷз§ҚзӢ¬зү№зҡ„жЁЎејҸеңЁж•°жҚ®еҢ…дј иҫ“дёӯеҸӘеҮәзҺ°дёҖж¬ЎгҖӮеҸҜд»ҘеҸ‘йҖҒж•°жҚ®еҢ…ж•°жҚ®пјҢд»ҘдҪҝеҠ жү°еҷЁиҫ“еҮәйҮҚеӨҚиҜҘжЁЎејҸгҖӮиҪҜ件дјҡйҷҗеҲ¶е№¶йҳ»жӯўиҜҘеҒҡжі•гҖӮ12дёӘиҝһз»ӯдҪҚй—ҙйҡ”зҡ„иҜҘзі»еҲ—еҗҢзӣёж•°жҚ®еәҸеҲ—з”ЁдәҺйҖҡиҝҮж—¶еәҸжҒўеӨҚжЁЎеқ—еӨҚдҪҚ并и·ҹиёӘжҺҘ收еҷЁж—¶еәҸе’ҢзӣёдҪҚгҖӮеӣ жӯӨпјҢе°ҶеӨҚдҪҚе…¶ж—¶еәҸи®Ўж•°еҷЁе№¶е°Ҷе…¶зӣёдҪҚеҖји®ҫзҪ®дёә0x1гҖӮиҜҘеәҸеҲ—еҗҺзҡ„第дёҖдёӘеҸҚиҪ¬иў«и§Ҷдёә0x0гҖӮеңЁжӯӨд№ӢеҗҺпјҢж—¶еәҸжҒўеӨҚжЁЎеқ—еңЁж•ҙдёӘж•°жҚ®еҢ…дј иҫ“иҝҮзЁӢдёӯдҝқжҢҒе…¶зҠ¶жҖҒдёҚеҸҳгҖӮ

ж•°жҚ®жҒўеӨҚжЁЎеқ—и®Ўз®—дҝЎеҸ·зҡ„е№іеқҮеҖјпјҢ并еҶіе®ҡдҝЎеҸ·зҡ„еҪ“еүҚзӣёдҪҚгҖӮ然еҗҺпјҢдёҺж—¶еәҸжҒўеӨҚжЁЎеқ—и·ҹиёӘзҡ„зӣёеҜ№зӣёдҪҚиҝӣиЎҢжҜ”иҫғгҖӮеҰӮжһңеҸ‘з”ҹеҶІзӘҒпјҢж №жҚ®иҝҮеҺ»зҡ„дҝЎеҸ·еҸҳеҢ–еҒҡеҶіе®ҡгҖӮиҝҷжҳҜеӣ дёәеҶІзӘҒйҖҡеёёжҳҜз”ұзӣёдҪҚеҲҮжҚўеј•иө·зҡ„гҖӮ

еӣҫ6. жҺҘ收数жҚ®и·Ҝеҫ„

然еҗҺпјҢи§Ји°ғзҡ„дҪҚж•°жҚ®з»„иЈ…еҲ°еӯ—иҠӮпјҢ并иҝӣиЎҢи§Јжү°гҖӮеҰӮжһңдј иҫ“зј“еҶІеҷЁдёәз©әпјҢеҲҷж•°жҚ®еҶҷе…Ҙдј иҫ“зј“еҶІеҷЁгҖӮеңЁж•°жҚ®еҢ…з»“жқҹж—¶йӘҢиҜҒCRCгҖӮеҰӮжһңеҢ№й…Қдё”дј иҫ“зј“еҶІеҷЁе·ІеҶҷе…ҘпјҢеҲҷйҖҡзҹҘеӨ„зҗҶеҷЁжҺҘеҸЈгҖӮиҪҜ件еә”еҪ“зӣ‘жҺ§иҜҘиҜ·жұӮпјҢеҰӮжһңе·Іи®ҫзҪ®пјҢйҖҡиҝҮиҜ»еҸ–е…¶еҶ…е®№жқҘжё…з©әзј“еҶІеҷЁгҖӮ然еҗҺпјҢеҝ…йЎ»жё…йҷӨиҜ·жұӮпјҢд»Ҙдҫҝ继з»ӯиҝӣиЎҢж•°жҚ®еҢ…дј иҫ“гҖӮ

жһ„е»әиҜҙжҳҺе’ҢдёӢиҪҪ

жң¬ж–Үд»Ӣз»Қз®ҖеҚ•RFеҹәеёҰеӨ„зҗҶеҷЁзҡ„зҗҶи®әе’Ңе®һж–ҪиҜҰжғ…гҖӮи®Ёи®әдәҶеңЁZC706е’ҢAD-FMCOMMS3-EBZ硬件дёҠе®һзҺ°иҜҘи®ҫи®Ўзҡ„е®һйҷ…ж–№жЎҲгҖӮеҝ«йҖҹжј”зӨәе’Ңжһ„е»әиҜҙжҳҺзҡ„е®Ңж•ҙи®ҫи®Ўж–Ү件еҸӮи§Ғhttps://wiki.analog.com/resources/fpga/docs/hdl/xcomm2ip гҖӮжӯӨйЎөйқўд№ҹиҜҰз»Ҷд»Ӣз»ҚдәҶHDLи®ҫи®ЎгҖҒиҪҜ件гҖҒRFи®ҫзҪ®гҖҒжҖ§иғҪе’ҢеҲҶжһҗгҖӮ

дҪңиҖ…з®Җд»Ӣ

Rejeesh KuttyдәҺ2011е№ҙеҠ е…ҘADIе…¬еҸёпјҢд»»е®ўжҲ·и§ЈеҶіж–№жЎҲж”ҜжҢҒйғЁй—Ёзҡ„HDLе·ҘзЁӢеёҲгҖӮд»–иҺ·еҫ—еҚ°еәҰ科еӯҰзҗҶе·ҘеӯҰйҷўзҡ„з”өеӯҗе·ҘзЁӢзЎ•еЈ«еӯҰдҪҚгҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·