为了测量高频率的S参数设计的设备,每个SBD被放置了有三个探头焊盘。中间信号垫的大小是85μm×85μm和顶部/底部的的地面尺寸是85μm×135μm的。使用GSG探头和网络分析仪,我们可以得到S参数设计的SBD.但是,S参数的直接测量结果包括垫片、金属线和覆盖的寄生电容。对于设计的设备而言,尽管寄生参数是非常小的,但这些寄生参数是绝对不能被忽视的,在计算的时候应该将GSG探头直接测量的S参数减去。在本文所研究的设计中,我们制作两个虚拟的GSG信号垫作为测试装置,假如两个信号垫一个是伪GSG信号垫,一个是SBD信号垫,且两个信号垫同等大小。除此以外的虚拟信号垫都是开放的,这也就是我们所说的开放式信号垫。S参数由哑垫进行测量。接着就可以得到信号垫和金属线的寄生电阻和电容。将这些寄生参数减去,就能够得到S参数的无寄生电阻和电容。将这种方法称之为去嵌入技术。

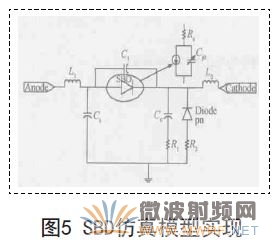

使用测得的S参数可以抽象为高频模拟SPICE模型。图5显示SBD仿真离子模型的实现。L1和L2显示出的输入和输出串联电感。Ci和Co表示阳极输入输出电容和阴极节点。C1具有相互交织的肖特基二极管的两个端口之间的寄生电容。R1和R2为连接S参数下NWLL到地面下电阻的n-阱的模型。pn二极管反映的寄生虫n阱p-次二极管。在我们的设计中,可以用得到的pn二极管的参数通过标准CMOS工艺0.35μm的SPICE模型。

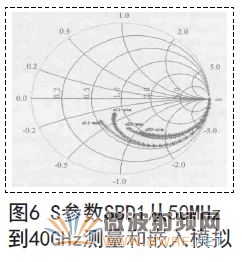

如图6所示,为S参数SBD1测量和模拟。

表2给出了仿真离子模型的参数,频率SBD1从50MHz到40GHz,该模型可以匹配到30GHz的测量结果。

6.结束语

随着无线通讯具有的灵活性和高机动性的特点,其应用越来越广泛,也顺应了市场的需求。由于CMOS工艺在诸多的工艺中最为成熟、成本最低,却功耗最小,因此得到广泛的应用,随着技术的不断成熟,CMOS工艺基础上的肖特基二极管设计及实现也成为现实。也是未来射频集成电路发展的必然趋势。通过MPW在标准CMOS工艺制造的肖特基势垒二极管中的设计应用,可知铝硅接触的势垒高度约0.44eV.

通过I-V,C-V和S参数测量可以实现SBD.通过本文所示,SBD设计的优势较为明显,最为显着的是设计成本较低,能够被广泛的应用与商业标准的CMOS工艺中。在以后的工作中,更多的重点将集中在标准CMOS工艺设计的SBD的反向击穿电压和频率范围扩展。

粤公网安备 44030902003195号

粤公网安备 44030902003195号