根据标准CMOS工艺基础上的肖特基二极管的布局及设计。首先,为了降低肖特基二极管的串联电阻,肖特基和欧姆接触电极之间的距离按照设计规则被设置为最小允许的距离。

其次,采用肖特基二极管布局的方法。交织式的布局为每一个串联电阻提供了并联连接的途径,这是肖特基接触的优势所在。

5.所制作的二极管的测定结果

根据MPW,对肖特基二极管的不同部位通过三种交织方法进行标准C M O S工艺下的0.35μm制造,并对测得的结果进行了讨论。

5.1 I-V的功能

基于对串联电阻的考虑,肖特基二极管的IV功能可表示为:

其中A*是有效的理查森常数。

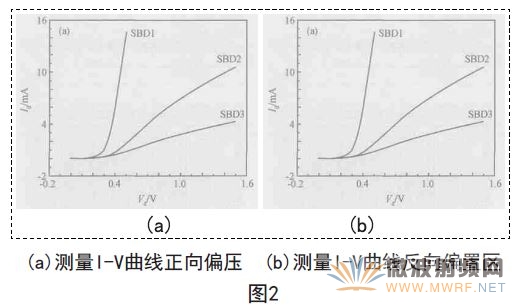

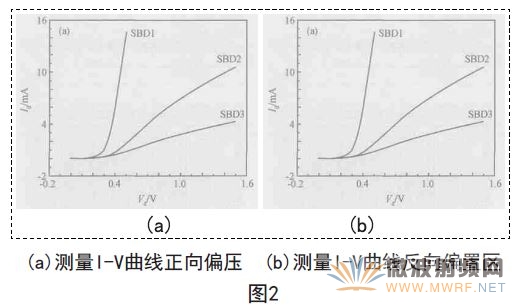

所测量的I-V曲线如图2所示。

(SBD1,SBD2,SBD3分别为16,1.6,0.64μm2)通过拟合公式(3)和所测得的结果,我们可以得到实现SBD的方法,如表1的参数所示。

从表1中可以观察到,随着相互交织的树木的增多,串联电阻的阻值明显的降低。

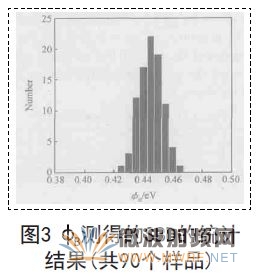

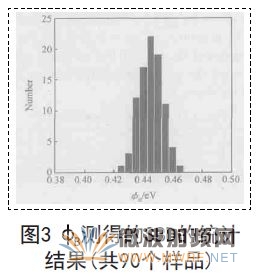

为实现SBD的测量,势垒高度B的测量的统计结果如图3所示。在所测的90个样本中,SBD1、SBD2、SBD3各30个样本,从而求得实现SBD的势垒高度为0.44eV左右。

击穿电压是4 . 5 V左右,在今后的工作中,在正常的SBD设计与生产中,击穿电压可以延长一些方法的使用,例如在自对准保护环境与SBD的制造过程中,5.2 C-V的功能

下面给出了小信号肖特基二极管的结电容Cj:

其中,Nd为掺杂浓度的n-阱,Φn是费米能级之间的电位差和导带边缘相等于(EC-Ef)/q.

图4显示了测得的反向偏压为SBD的C-V曲线。

粤公网安备 44030902003195号

粤公网安备 44030902003195号