接着对整机进行测试,结果如下:

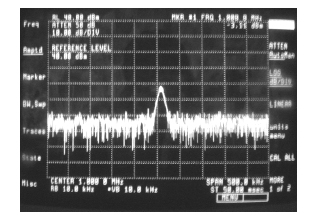

图7、实际解调输出信号

解调输出后得到信号频率为1MHz 的基带信号。固定AGC 增益值的情况下,即此时衰减值固定为0dBm,改变输入射频信号的功率,每增加10dBm,输出I/Q 信号功率增加约为10dBm,整机线性度[10]良好,注意此时应该在较低功率范围内调节输入功率,保证输出I/Q信号功率不会过大。经测试,接收机的最小可接收检测信号功率约-118dBm。

在接收机中,解调输出I/Q 两路平衡是非常重要的指标。由于接收机信道特性不同,本振信号相位误差等诸多的因素都会导致I/Q 两路基带信号增益不平衡。若I/Q 失配,则会导致I/Q 误码率增高,严重影响解调性能。在本设计中,在选取芯片、设计电路中充分考虑到此问题,实际I/Q 两路输出基本做到了平衡输出。

5、结论

本文研究了使用PLL 的接收机原理和实现方案,并成功的用软硬件平台对其实现。本文的创新点在于成功的运用两个锁相环电路实现第一、二本振信号,试验结果表明锁相环有锁定时间短,相位噪声小,性能稳定等优点。实测结果表明接收机性能良好,指标达到了系统设计要求。

现代射频接收机主要是向高线性、大动态范围,高灵敏度,高分辨率等方面发展。如何采取有效的方法来提高接收机的抗干扰能力,降低超外差式接收机的成本,使得整体性能得以改进,是当今研究的热点方向,对接收机的研究有着非常重要的意义。

作者:牛吉凌,孙利佳

参考文献

[1] Roy B.《无线通信技术》[M].北京:科学出版社,2004.

[2] 张玉兴.《射频模拟技术》[M].北京:电子工业出版社,2001.

[3] 陈邦媛.《射频通信电路》[M].北京:科学出版社,2002.

[4] 张猛,章策珉,马金军,楼东武.射频接收机整体噪声与增益可预测性设计[J].无线电工程, 2000,1(2): 13-17.

[5] 张厥盛,郑继禹.《锁相技术》[M].西安:西安电子科技大学出版社,1996.

[6] Behzard R,

[7] Integrated synthesizer and VCO ADF4360-8, Analog Devices C04414-0-12/04(B), 2004.

[8] Derek K S, The design and implementation of low-power CMOS radio receivers [J]. PhD Thesis, 1998, 17(2):41-46.

[9] Reinhold L P,

[10] Gonzalez G, Micro transistor amplifiers: analysis and design [J]. Englewood Cliffs, NJ: Pretice-Hall, 1984:91-44.

粤公网安备 44030902003195号

粤公网安备 44030902003195号