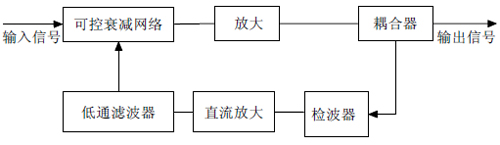

图2、AGC 电路原理图

3.2、接收机本振锁相环路的设计

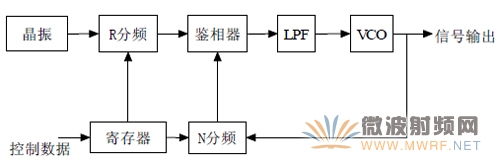

图3、琐相环原理图

接收机通过混频实现射频变频到基带,而且采用的是超外差式结构的接收机,因此在本设计中我们需要设计两个本振源。系统设计要求本振信号频率精度和稳定度高,相位噪声小,所以选择锁相环实现本振生成。锁相环是一种建立在相位负反馈基础之上的闭环控制系统[5],对相位噪声和杂散具有很好的抑制作用,在电视,仪器,通信等领域得到了广泛的应用。该接收机本振设计我们采用ADI 公司的琐相环系列芯片[6-7]做本振的设计,其可应用于无线射频通信系统,是性价比很高的电荷泵锁存芯片。

在设计中,通过编写程序由单片机实现提供给琐相环的CLOCK,DATA 和LE 信号,在频率合成器芯片内部完成参考晶振R 分频和压控振荡器N 分频相位的比较,并且转换成相应的线性电压后,经过3 阶环路滤波器滤出高频干扰信号后,得到一个稳定电压来控制压控振荡器的输出,最终的信号频率通过两个锁相芯片被分别锁定在第一和第二本振频率上。

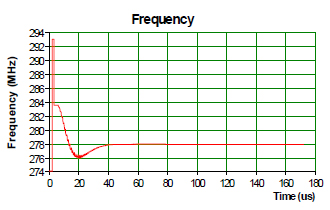

图4、第二本振的琐相环入琐过程

从图4,第二本振的入锁过程我们可以看到琐相环的入锁时间在40us 左右,满足要求。采用单片机提供锁相的控制字的优点就在于:利于及时修改,便于操作。下面是本振的实际电路图,包括第一本振锁相芯片和第二本振锁相芯片,其共用一个10MHz 的晶振:

图5 实际的第一、第二本振电路图

3.3、解调

接收机解调部分采用AD 公司的解调芯片,该芯片工作频率从50MHz 到1000MHz,包括正交下变频器,内置可控增益放大器和偏置电路。其内置VGA,控制电压由外部提供并可调增益大小,增益可调范围为44dB。

输入芯片的中频信号为了满足芯片的输入功率要求,加入了功率驱动放大链路,经放大后输入解调芯片的功率约为-40dBm 左右。因为解调芯片对第二本振信号内置了二分频器,所以第二本振信号频率应该是所需频率的两倍。

输出的I/Q 两路信号分别再经过运放电路进行放大,最终输出给数字基带部分进行处理[8-9]。

4、实际测试结果

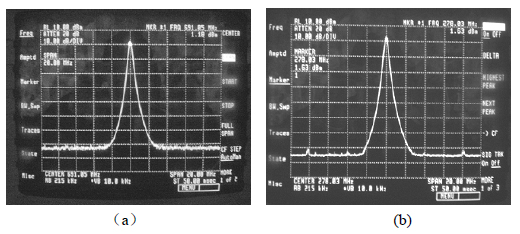

实际测时,输入信号频率为831MHz,通过在单片机编写控制字程序设置第一本振和第二本振的输出频率,第一次混频后得到的中频信号频率为140MHz,第二次混频后解调输出频率为1MHz 的I/Q 两路信号。本振的输出信号如下图所示:

图6、(a)第一本振输出(b)第二本振输出

粤公网安备 44030902003195号

粤公网安备 44030902003195号