зҪ‘з«ҷйҰ–йЎө > жҠҖжңҜж–Үеә“ > RFIC >

еҹәдәҺIQи§Ји°ғеҷЁпјҢе…·жңүдёӯйў‘е’ҢеҹәеёҰеҸҜеҸҳеўһзӣҠд»ҘеҸҠеҸҜзј–зЁӢеҹәеёҰж»ӨжіўеҠҹиғҪзҡ„дёӯйў‘иҮіеҹәеёҰжҺҘ收жңә

з”өи·ҜеҠҹиғҪдёҺдјҳеҠҝ

иҜҘз”өи·ҜжҳҜзҒөжҙ»зҡ„йў‘зҺҮжҚ·еҸҳдёӯйў‘иҮіеҹәеёҰжҺҘ收жңәгҖӮдёӯйў‘е’ҢеҹәеёҰдёҠзҡ„еҸҜеҸҳеўһзӣҠз”ЁдәҺи°ғж•ҙдҝЎеҸ·з”өе№ігҖӮ ADRF6510 еҹәеёҰADCй©ұеҠЁеҷЁиҝҳеҢ…жӢ¬еҸҜзј–зЁӢдҪҺйҖҡж»ӨжіўеҷЁпјҢеҸҜж¶ҲйҷӨйҖҡйҒ“еӨ–йҳ»еЎһе’ҢеҷӘеЈ°гҖӮ

жӯӨж»ӨжіўеҷЁзҡ„еёҰе®ҪеҸҜйҡҸзқҖиҫ“е…ҘдҝЎеҸ·еёҰе®ҪеҸҳеҢ–иҖҢеҠЁжҖҒең°и°ғиҠӮгҖӮиҝҷж ·еҸҜд»ҘзЎ®дҝқз”ұжң¬з”өи·Ҝй©ұеҠЁзҡ„ADCзҡ„еҸҜз”ЁеҠЁжҖҒиҢғеӣҙеҫ—еҲ°е……еҲҶдҪҝз”ЁгҖӮ

з”өи·ҜеҶ…ж ёжҳҜIQи§Ји°ғеҷЁгҖӮ ADL5387 еҹәдәҺ2Г—LOзҡ„зӣёдҪҚеҲҶзҰ»жһ¶жһ„ж”ҜжҢҒе®Ҫйў‘зҺҮиҢғеӣҙе·ҘдҪңгҖӮзІҫзЎ®зҡ„жӯЈдәӨе№іиЎЎе’ҢдҪҺиҫ“еҮәзӣҙжөҒеӨұи°ғзЎ®дҝқдәҶеҜ№иҜҜе·®зҹўйҮҸе№…еәҰ(EVM)зҡ„еҪұе“ҚжһҒе°ҸгҖӮ

жң¬з”өи·ҜеҶ…жүҖжңүе…ғ件й—ҙзҡ„жҺҘеҸЈеқҮйҮҮз”Ёе…Ёе·®еҲҶејҸгҖӮеҰӮжһңдёҚеҗҢзә§й—ҙйңҖиҰҒзӣҙжөҒиҖҰеҗҲпјҢзӣёйӮ»зә§зҡ„еҒҸзҪ®з”өе№іеҪјжӯӨе…је®№гҖӮ

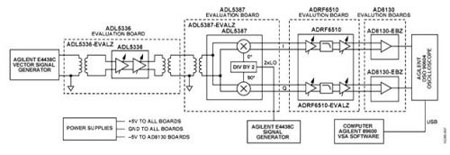

еӣҫ1. зӣҙжҺҘеҸҳйў‘жҺҘ收жңәеҺҹзҗҶзӨәж„Ҹеӣҫ(жүҖжңүиҝһжҺҘе’ҢеҺ»иҖҰеқҮжңӘжҳҫзӨә)

з”өи·ҜжҸҸиҝ°

жҺҘ收жңәжһ¶жһ„

жң¬з”өи·Ҝ笔记дёӯжҸҸиҝ°дәҶжҺҘ收жңәзҡ„зӣҙжҺҘеҸҳйў‘(д№ҹз§°дёәйӣ¶е·®жҲ–йӣ¶дёӯйў‘)жһ¶жһ„гҖӮдёҺеҸҜд»Ҙжү§иЎҢеӨҡж¬Ўйў‘зҺҮиҪ¬жҚўзҡ„и¶…еӨ–е·®ејҸжҺҘ收жңәзӣёжҜ”пјҢзӣҙжҺҘеҸҳйў‘ж— зәҝз”өеҸӘиғҪжү§иЎҢдёҖж¬Ўйў‘зҺҮиҪ¬жҚўгҖӮдёҖж¬Ўйў‘зҺҮиҪ¬жҚўзҡ„дјҳеҠҝеҰӮдёӢпјҡ

- йҷҚдҪҺжҺҘ收жңәеӨҚжқӮжҖ§пјҢеҮҸе°‘жүҖйңҖзә§ж•°пјӣжҸҗй«ҳжҖ§иғҪе’ҢйҷҚдҪҺеҠҹиҖ—

- йҒҝе…Қй•ңеғҸжҠ‘еҲ¶й—®йўҳе’ҢдёҚйңҖиҰҒзҡ„ж··йў‘дә§зү©пјӣеҸӘйңҖиҰҒеҹәеёҰдёҠзҡ„дёҖдёӘLPF

- й«ҳзҒөж•ҸеәҰ(зӣёйӮ»йҖҡйҒ“жҠ‘еҲ¶жҜ”[ACRR])

еӣҫ1жҳҫзӨәдәҶиҜҘзі»з»ҹзҡ„еҹәжң¬еҺҹзҗҶзӨәж„ҸеӣҫпјҢеҢ…жӢ¬йӣҶжҲҗиҮӘеҠЁеўһзӣҠжҺ§еҲ¶(AGC)зҺҜи·Ҝзҡ„зә§иҒ”дёӯйў‘еҸҜеҸҳеўһзӣҠж”ҫеӨ§еҷЁ(VGA)пјҢд»ҘеҸҠзҙ§йҡҸе…¶еҗҺзҡ„жӯЈдәӨи§Ји°ғеҷЁгҖҒе…·жңүеҸҜеҸҳеҹәеёҰеўһзӣҠзҡ„еҸҜзј–зЁӢдҪҺйҖҡж»ӨжіўеҷЁгҖӮеӣҫ1дёӯд»ҘзҒ°иүІжҳҫзӨәзҡ„е…ғ件( ADF4350 е’Ң AD9248) жҳҜдёәжё…жҘҡиө·и§ҒпјҢ并дёҚеҢ…жӢ¬еңЁзі»з»ҹзә§жөӢйҮҸдёӯ(жңүе…іиҝҷдәӣеҷЁд»¶зҡ„иҜҰжғ…иҜ·еҸӮи§ҒвҖңеёёи§ҒеҸҳеҢ–вҖқйғЁеҲҶ)гҖӮ

зҗҶжғіжғ…еҶөдёӢпјҢ第дёҖзә§зҡ„иҫ“е…Ҙе’ҢжңҖеҗҺзә§зҡ„иҫ“еҮәеә”и®ҫзҪ®зі»з»ҹзҡ„еҠЁжҖҒиҢғеӣҙ(дҝЎеҷӘжҜ”)гҖӮе®һйҷ…дёҠпјҢжғ…еҶөеҸҜиғҪ并йқһеҰӮжӯӨгҖӮеңЁжӯЈдәӨи§Ји°ғеҷЁд№ӢеүҚж”ҫзҪ®зә§иҒ”VGAдёҚд»…дјҡз»ҷзі»з»ҹеёҰжқҘжӣҙеӨҡеўһзӣҠпјҢиҖҢдё”жңүеҲ©дәҺж•ҙдҪ“зі»з»ҹеҷӘеЈ°жҖ§иғҪпјҢеҸӘиҰҒVGAзҡ„еҷӘеЈ°зі»ж•°дҪҺдәҺжӯЈдәӨи§Ји°ғеҷЁпјҢеҸӘиҰҒVGAд»Қе…·жңүеўһзӣҠпјҢдё”жңӘеҸ‘з”ҹиЎ°еҮҸгҖӮеҗҺз»ӯзә§зҡ„еҷӘеЈ°зі»ж•°йҖҡиҝҮеҲқе§ӢVGAзҡ„еўһзӣҠиҝӣиЎҢеҲҶйў‘еӨ„зҗҶгҖӮжҸҗдҫӣVGA (зӣёеҜ№дәҺд»…жҸҗдҫӣеӣәе®ҡеўһзӣҠж”ҫеӨ§еҷЁ)зҡ„еҸҰдёҖдјҳзӮ№жҳҜAGCзҺҜи·ҜеҸҜз»Ҹи®ҫи®Ўд»Ҙи°ғе№іжӯЈдәӨи§Ји°ғеҷЁзҡ„иҫ“е…ҘдҝЎеҸ·гҖӮиҝҷдёҖйҷҗеҲ¶ж–ҪеҠ дәҺжӯЈдәӨи§Ји°ғеҷЁе’Ңд»»дҪ•еҗҺз»ӯзә§зҡ„дҝЎеҸ·з”өе№ізҡ„иғҪеҠӣйқһеёёйҮҚиҰҒгҖӮ

дёӯйў‘VGAе’ҢAGCзҺҜи·Ҝ

дёӯйў‘VGAе’ҢAGCзҺҜи·ҜеҠҹиғҪеҸҜйҖҡиҝҮ ADL5336жқҘе®һзҺ°гҖӮе®ғе…·жңүдёӨдёӘеҸҜзә§иҒ”VGAпјҢжҜҸдёӘVGAе…·жңү24 dBзҡ„жЁЎжӢҹеҠЁжҖҒиҢғеӣҙпјҢ并且еҸҜд»ҘйҖҡиҝҮSPIз«ҜеҸЈд»Ҙж•°еӯ—ж–№ејҸж”№еҸҳжҜҸдёӘVGAдёҠзҡ„жңҖеӨ§еўһзӣҠгҖӮ

дёәдәҶе®һзҺ°дҝЎеҸ·и°ғе№іAGCеҠҹиғҪпјҢжҜҸдёӘ ADL5336 VGAе…·жңүе№іж–№еҫӢжЈҖжіўеҷЁпјҢйҖҡиҝҮеҸҜзј–зЁӢиЎ°еҮҸеҷЁиҝһжҺҘеҲ°иҫ“еҮәгҖӮжЈҖжіўеҷЁе°ҶиЎ°еҮҸеҷЁзҡ„иҫ“еҮәдёҺ63 mV rmsзҡ„еҶ…йғЁеҹәеҮҶз”өеҺӢиҝӣиЎҢжҜ”иҫғгҖӮеҰӮжһңиЎ°еҮҸеҷЁиҫ“еҮәдёҺ63 mV rmsеҹәеҮҶз”өеҺӢй—ҙжңүе·®ејӮпјҢиҜҜе·®з”өжөҒдҫҝдјҡдә§з”ҹ并йӣҶжҲҗеҲ°CAGCз”өе®№еҶ…гҖӮAGCзҺҜи·ҜйҖҡиҝҮе°ҶDTO1/DTO2еј•и„ҡиҝһжҺҘеҲ°GAIN1/GAIN2еј•и„ҡе…ій—ӯгҖӮдёәдәҶдҪҝAGCзҺҜи·ҜжӯЈеёёе·ҘдҪңпјҢе°ҶMODEеј•и„ҡжӢүиҮідҪҺз”өе№іпјҢд»ҺиҖҢдә§з”ҹиҙҹVGAеўһзӣҠж–ңзҺҮгҖӮ

жҜҸдёӘ ADL5336 VGAе…·жңүе…Ғи®ёзҡ„иҫ“е…ҘеҠҹзҺҮиҢғеӣҙпјҢAGCе°ҶеңЁжӯӨиҢғеӣҙеҶ…и°ғе№іиҮізү№е®ҡи®ҫе®ҡзӮ№гҖӮеңЁиҜҘиҢғеӣҙд»ҘеӨ–пјҢVGAиҫ“еҮәйҡҸиҫ“е…ҘдёҖиө·жҢүdBйҖ’еўһжҲ–йҖ’еҮҸ(еҒҮе®ҡVGAжңӘеӨ„дәҺеҺӢзј©зҠ¶жҖҒжҲ–дҝЎеҸ·дёҚеңЁеҷӘеә•еҶ…)гҖӮ

IQи§Ји°ғеҷЁ

дҝЎеҸ·д»Һ ADL5336 и·Ҝз”ұиҮі ADL5387пјҢеңЁжӯӨжҺҘеҸ—и§Ји°ғ并е°Ҷйў‘зҺҮиҪ¬жҚўдёәйӣ¶дёӯйў‘гҖӮ ADF4350 йў‘зҺҮеҗҲжҲҗеҷЁеҸҜеҗ‘ ADL5387жҸҗдҫӣжүҖйңҖзҡ„2Г—LOдҝЎеҸ·(еҸӮи§ҒвҖңеёёи§ҒеҸҳеҢ–вҖқйғЁеҲҶ)пјӣдҪҶе®һйҷ…жөӢиҜ•дҪҝз”ЁдҝЎеҸ·еҸ‘з”ҹеҷЁд»Јжӣҝ ADF4350 гҖӮ

ADL5387 дҪҝз”ЁдёӨдёӘеҸҢе№іиЎЎж··йў‘еҷЁпјҢдёҖдёӘз”ЁдәҺIйҖҡйҒ“пјҢдёҖдёӘз”ЁдәҺQйҖҡйҒ“гҖӮжҸҗдҫӣз»ҷж··йў‘еҷЁзҡ„LOдҪҝз”Ё2еҲҶйў‘жӯЈдәӨеҲҶзӣёеҷЁз”ҹжҲҗгҖӮиҝҷдёәIе’ҢQйҖҡйҒ“жҸҗдҫӣдәҶ0В°е’Ң90В°дҝЎеҸ·гҖӮ ADL5387еңЁRFиҫ“е…ҘиҮіеҹәеёҰIе’ҢQиҫ“еҮәд№Ӣй—ҙжҸҗдҫӣзәҰ4.5 dBзҡ„иҪ¬жҚўеўһзӣҠгҖӮ

дҪҺйҖҡж»ӨжіўеҷЁгҖҒеҹәеёҰVGAе’ҢADCй©ұеҠЁеҷЁ

дҪҺйҖҡж»ӨжіўгҖҒеҹәеёҰеўһзӣҠе’ҢADCй©ұеҠЁеҷЁеҠҹиғҪе…ЁйғЁдҪҝз”Ё ADRF6510жқҘе®һзҺ°гҖӮж–ҪеҠ дәҺ ADRF6510 зҡ„дҝЎеҸ·зҺ°еңЁе…·жңүзӢ¬з«Ӣзҡ„Iе’ҢQи·Ҝеҫ„пјҢдҝЎеҸ·йҰ–е…ҲйҖҡиҝҮеүҚзҪ®ж”ҫеӨ§еҷЁж”ҫеӨ§пјҢ然еҗҺиҝӣиЎҢдҪҺйҖҡж»ӨжіўпјҢд»ҘжҠ‘еҲ¶д»»дҪ•дёҚйңҖиҰҒзҡ„еёҰеӨ–дҝЎеҸ·е’Ң/жҲ–еҷӘеЈ°пјҢжңҖеҗҺйҖҡиҝҮVGAж”ҫеӨ§гҖӮ

ADRF6510 зҡ„жҜҸдёӘйҖҡйҒ“еҸҜеҲҶдёәдёүдёӘзә§пјҡ

- еүҚзҪ®ж”ҫеӨ§еҷЁ

- еҸҜзј–зЁӢдҪҺйҖҡж»ӨжіўеҷЁ

- VGAе’Ңиҫ“еҮәй©ұеҠЁеҷЁ

йҖҡиҝҮGNSWеј•и„ҡпјҢеүҚзҪ®ж”ҫеӨ§еҷЁе…·жңү6dBжҲ–12dBзҡ„з”ЁжҲ·еҸҜйҖүеўһзӣҠгҖӮдҪҺйҖҡж»ӨжіўеҷЁеҸҜйҖҡиҝҮSPIз«ҜеҸЈи®ҫзҪ®дёә1MHzиҮі30MHzзҡ„иҪ¬жҠҳйў‘зҺҮпјҢжӯҘиҝӣдёә1MHzгҖӮVGAе…·жңү50dBеўһзӣҠиҢғеӣҙпјҢеўһзӣҠж–ңзҺҮдёә30mV/dBгҖӮVGAеўһзӣҠйҖҡиҝҮGAINеј•и„ҡжҺ§еҲ¶пјҢGNSWеј•и„ҡиў«жӢүдҪҺж—¶иҢғеӣҙеҸҜдёә0.5dBиҮі+45dBпјҢGNSWеј•и„ҡиў«жӢүй«ҳж—¶иҢғеӣҙеҸҜдёә+1dBиҮі+51dBгҖӮиҫ“еҮәй©ұеҠЁеҷЁиғҪеӨҹе°Ҷ1.5Vppе·®еҲҶз”өеҺӢй©ұеҠЁиҮі1kиҙҹиҪҪеҶ…пјҢеҗҢж—¶дҝқжҢҒй«ҳдәҺ60dBcзҡ„HD2е’ҢHD3гҖӮ

еҸҜж–ҪеҠ дәҺдҪҺйҖҡж»ӨжіўеҷЁеҗҢж—¶д»ҚеңЁ ADRF6510еҶ…дҝқжҢҒеҸҜжҺҘеҸ—зҡ„HDз”өе№ізҡ„жңҖеӨ§CWдҝЎеҸ·дёә2VppгҖӮеҰӮжһңеӯҳеңЁиҫғеӨ§еёҰеӨ–е№Іжү°жәҗдё”еҸҜиғҪйҖ жҲҗ ADL5387 е’Ң/жҲ–ADRF6510зҡ„иҫ“е…ҘиҝҮиҪҪпјҢеёҰеӨ–е№Іжү°жәҗ(еҸҠжүҖйңҖзҡ„еёҰеҶ…дҝЎеҸ·)еҸҜйҖҡиҝҮ ADL5336VGAдәҲд»ҘиЎ°еҮҸгҖӮ дёҖж—ҰеёҰеӨ–е№Іжү°жәҗиў«ADRF6510зҡ„дҪҺйҖҡж»ӨжіўеҷЁжҠ‘еҲ¶пјҢжүҖйңҖдҝЎеҸ·еҸҜдҪҝз”ЁXAMPVGA(зҙ§йҡҸ ADRF6510зҡ„ж»ӨжіўеҷЁ)ж”ҫеӨ§гҖӮ

ADRF6510еҸ‘еҮәзҡ„IQдҝЎеҸ·еҸҜж–ҪеҠ дәҺйҖӮеҪ“зҡ„жЁЎж•°иҪ¬жҚўеҷЁ(ADC)пјҢдҫӢеҰӮAD9248гҖӮ

жөӢйҮҸз»“жһң

4-QAMгҖҒ5 MSPSи°ғеҲ¶дҝЎеҸ·иў«ж–ҪеҠ дәҺADL5336зҡ„иҫ“е…ҘгҖӮжңүе…іжөӢиҜ•и®ҫзҪ®зҡ„жӣҙеӨҡдҝЎжҒҜпјҢиҜ·еҸӮи§ҒвҖңз”өи·ҜиҜ„дј°е’ҢжөӢиҜ•вҖқйғЁеҲҶгҖӮ

EVMиЎЎйҮҸж•°еӯ—еҸ‘е°„жңәжҲ–жҺҘ收жңәзҡ„жҖ§иғҪиҙЁйҮҸпјҢеҸҚжҳ е№…еәҰе’ҢзӣёдҪҚиҜҜе·®жүҖеҜјиҮҙзҡ„е®һйҷ…жҳҹеә§зӮ№дёҺзҗҶжғідҪҚзҪ®зҡ„еҒҸе·®гҖӮеҰӮеӣҫ2жүҖзӨәгҖӮ

еӣҫ2. EVMеӣҫ

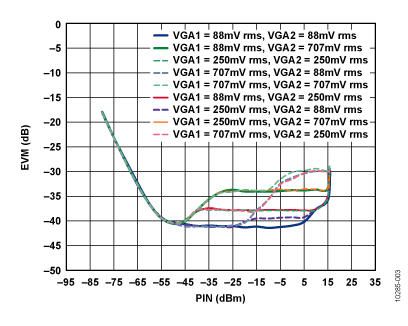

еӣҫ3жҳҫзӨәдәҶзі»з»ҹEVMдёҺADL5336иҫ“е…ҘеҠҹзҺҮзҡ„е…ізі»пјҢVGAдёҠзҡ„жңҖеӨ§еўһзӣҠй’ҲеҜ№VGA1е’ҢVGA2еҲҶеҲ«и®ҫзҪ®дёә15.2dBе’Ң19.5dBгҖӮ

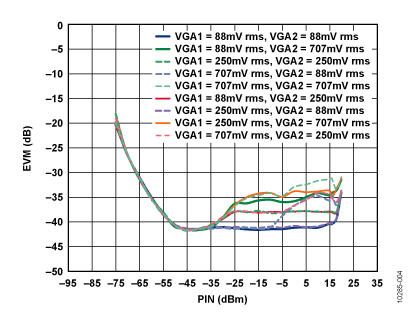

жөӢиҜ•дәҶж•°дёӘAGCи®ҫе®ҡзӮ№з»„еҗҲгҖӮеӣҫ4д№ҹжҳҜзі»з»ҹEVMдёҺADL5336иҫ“е…ҘеҠҹзҺҮзҡ„е…ізі»пјӣдёҚиҝҮVGAзҡ„еўһзӣҠеҲҶеҲ«и®ҫзҪ®дёә9.7dBе’Ң13.4dBгҖӮжөӢиҜ•дәҶзӣёеҗҢзҡ„AGCи®ҫе®ҡзӮ№з»„еҗҲгҖӮ

еӣҫ3. зі»з»ҹEVMпјҢж•°еӯ—VGAеўһзӣҠ=11

еӣҫ4. зі»з»ҹEVMпјҢж•°еӯ—VGAеўһзӣҠ=00

еӣҫ3е’Ңеӣҫ4иҜҙжҳҺпјҢж–ҪеҠ дәҺ ADRF6510 зҡ„дҝЎеҸ·з”өе№іеҝ…йЎ»дҝқжҢҒи¶і еӨҹдҪҺд»Ҙе…ҚеҺӢзј©иҫ“е…Ҙзә§е’Ң/жҲ–ж»ӨжіўеҷЁгҖӮеңЁжңҖй«ҳAGCи®ҫе®ҡзӮ№ (500mVrmsе’Ң707mVrms)пјҢ ADL5387IQи§Ји°ғеҷЁзҡ„иҫ“е…ҘејҖе§ӢеҺӢ缩并з»ҷEVMйҖ жҲҗйўқеӨ–дёӢйҷҚгҖӮеҪ“AGCи®ҫе®ҡзӮ№дҪҚдәҺжңҖдҪҺзӮ№ (88mVrms)ж—¶пјҢеҸҜе®һзҺ°жңҖдҪіEVMгҖӮеҪ“и®ҫе®ҡзӮ№дёә250mVrms ж—¶пјҢEVMе·Із»ҸејҖе§ӢдёӢйҷҚгҖӮ

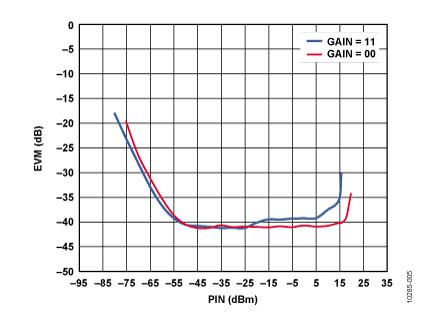

еӣҫ5жҜ”иҫғдәҶ ADL5336VGAдёҠзҡ„жңҖе°Ҹе’ҢжңҖеӨ§ж•°еӯ—еўһзӣҠи®ҫзҪ®(VGA еқҮи®ҫзҪ®дёәеўһзӣҠд»Јз Ғ11жҲ–еўһзӣҠд»Јз Ғ00)й—ҙзҡ„EVMпјҢжӯӨж—¶VGA1 е’ҢVGA2и®ҫе®ҡзӮ№еҲҶеҲ«дёә250 mVrmsе’Ң88 mVrmsгҖӮ

еӣҫ5. зі»з»ҹEVMпјҢVGA1и®ҫе®ҡзӮ№=250MVRMSпјҢVGA2и®ҫе®ҡзӮ№=88MVRMS

еҜ№дәҺз»ҷе®ҡAGCи®ҫе®ҡзӮ№пјҢеҪ“жңҖеӨ§еўһзӣҠд»Јз Ғдёә11ж—¶пјҢд»ҺVGA2 иҮіVGA1зҡ„еҲҮжҚўеңЁVGA2и¶…еҮәеўһзӣҠиҢғеӣҙеҗҺеҸ‘з”ҹпјӣеӣ жӯӨпјҢж–ҪеҠ дәҺ ADRF6510 зҡ„дҝЎеҸ·з”ө平继з»ӯеўһеҠ (еҗҢж—¶EVMдёӢйҷҚ)пјҢзӣҙиҮі VGA1еҲ°иҫҫи®ҫе®ҡзӮ№гҖӮдёҖж—ҰVGA1еҲ°иҫҫи®ҫе®ҡзӮ№пјҢEVMеҶҚж¬ЎеҸҳе№іпјӣеӣ жӯӨж–ҪеҠ дәҺ ADRF6510 зҡ„дҝЎеҸ·з”өе№іеңЁеӨ§зәҰ5 dBmзҡ„иҫ“е…ҘеҠҹзҺҮдёӢдёҚдјҡеҸҳеҢ–пјҢйҷӨйқһVGA1и¶…еҮәеўһзӣҠиҢғеӣҙгҖӮеҪ“жңҖеӨ§еўһзӣҠд»Јз Ғи®ҫзҪ®дёә00ж—¶пјҢVGAеқҮеҸҜжҸҗдҫӣжӣҙеӨҡиЎ°еҮҸпјҢеӣ жӯӨе…Ғи®ёVGA2еҒҸ移еҠЁжҖҒиҢғеӣҙпјҢд»Ҙе…ҚеңЁиҫ“е…ҘеҠҹзҺҮдҪҺиҮідёҺжңҖеӨ§еўһзӣҠд»Јз Ғдёә11ж—¶зӣёеҗҢзҡ„жғ…еҶөдёӢеҲ°иҫҫи®ҫе®ҡзӮ№гҖӮиҝҷж ·VGA2еҸҜеңЁиҫғй«ҳиҫ“е…ҘеҠҹзҺҮдёӢдҝқжҢҒеңЁи®ҫе®ҡзӮ№пјҢдҪҝVGA2иҮіVGA1зҡ„еҲҮжҚўеҸҜеҸ‘з”ҹеңЁVGA2и¶…еҮәеўһзӣҠиҢғеӣҙд№ӢеүҚгҖӮиҝҷж ·е°ұиғҪзЎ®дҝқж–ҪеҠ дәҺ ADRF6510зҡ„дҝЎеҸ·з”өе№ідҝқжҢҒеңЁжҒ’е®ҡеҖјпјҢзӣҙиҮіеҲ°иҫҫиҫ“е…ҘеҠҹзҺҮиҢғеӣҙжңҖй«ҳзӮ№гҖӮ

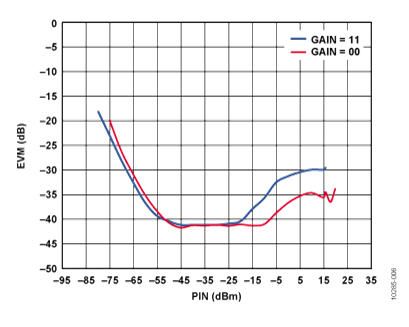

еӣҫ6жҜ”иҫғдәҶ ADL5336 VGAдёҠзҡ„жңҖе°Ҹе’ҢжңҖеӨ§ж•°еӯ—еўһзӣҠи®ҫзҪ®(VGA еқҮи®ҫзҪ®дёәеўһзӣҠд»Јз Ғ11жҲ–еўһзӣҠд»Јз Ғ00)й—ҙзҡ„EVMпјӣдёҚиҝҮVGA1 е’ҢVGA2и®ҫе®ҡзӮ№еҲҶеҲ«дёә707mVrmsе’Ң88mVrmsгҖӮ

еӣҫ6. зі»з»ҹEVMпјҢVGA1и®ҫе®ҡзӮ№=707MVRMSпјҢVGA2и®ҫе®ҡзӮ№=88MVRMS

еӣҫ6дёӯзҡ„еҠЁжҖҒзү№жҖ§дёҺеӣҫ5зӣёеҗҢпјҢеҸӘдёҚиҝҮжӣҙдёәеӨёеј гҖӮеҪ“жңҖеӨ§еўһзӣҠд»Јз Ғдёә00ж—¶пјҢVGA2еңЁзәҰ-40dBmзҡ„иҫ“е…ҘеҠҹзҺҮдёӢеҲ°иҫҫи®ҫе®ҡзӮ№гҖӮе…¶дҝқжҢҒи®ҫе®ҡзӮ№иҮізәҰ-10dBmпјҢжӯӨж—¶VGA1е°ҡжңӘеҲ°иҫҫ707mVrmsзҡ„и®ҫе®ҡзӮ№гҖӮйҷӨйқһиҫ“е…ҘеҠҹзҺҮзәҰдёә0dBmпјҢ并且EVMејҖе§Ӣз•Ҙеҫ®еҸҳе№іпјҢеҗҰеҲҷVGA1дёҚдјҡеҲ°иҫҫи®ҫе®ҡзӮ№гҖӮеҪ“жңҖеӨ§еўһзӣҠи®ҫзҪ®дёә11ж—¶пјҢзӣёеҗҢжғ…еҶөеҶҚж¬ЎеҸ‘з”ҹпјӣдёҚиҝҮпјҢVGA2д»…дҝқжҢҒи®ҫе®ҡзӮ№иҮіеӨ§зәҰ-20dBmпјҢеӣ дёәеҶҚж— жӣҙеӨҡеўһзӣҠеҸҜз”ЁдәҺиҺ·еҫ—规е®ҡзҡ„и®ҫе®ҡзӮ№гҖӮ

еёёи§ҒеҸҳеҢ–

зі»з»ҹе’Ңйў‘зҺҮеҗҲжҲҗеҷЁ

дёә ADL5387жҸҗдҫӣ2XLOзҡ„дҝЎеҸ·еҸ‘з”ҹеҷЁеҸҜиў«е®ҪеёҰйў‘зҺҮеҗҲжҲҗеҷЁеҸ– д»ЈпјҢдҫӢеҰӮ ADF4350пјҢиҜҘеҷЁд»¶йӣҶжҲҗдәҶVCOгҖӮ ADF4350 еұһдәҺдёҖдёӘйў‘зҺҮеҗҲжҲҗеҷЁзі»еҲ—пјҢиҜҘзі»еҲ—е…·жңү135MHzиҮі4350MHzзҡ„е®Ҫйў‘зҺҮиҢғеӣҙпјҢдё”е…·жңүеҸҳеҢ–зҡ„зӣёдҪҚеҷӘеЈ°е’Ңиҫ“еҮәеҠҹзҺҮжҢҮж ҮпјҢеӣ жӯӨеҫҲе®№жҳ“жүҫеҲ°з¬ҰеҗҲеә”з”ЁжүҖйңҖи§„ж јзҡ„еҷЁд»¶гҖӮ

зі»з»ҹе’ҢADC

дёәзі»з»ҹж·»еҠ ADCд»ҘеҜ№ ADRF6510зҡ„Iе’ҢQдҝЎеҸ·иҝӣиЎҢйҮҮж ·жӯЈжҳҜе®Ңе–„жЁЎжӢҹдҝЎеҸ·й“ҫиҮӘ然演еҢ–зҡ„з»“жһңгҖӮеҸҢйҖҡйҒ“ADCпјҢдҫӢеҰӮ AD9248пјҢжҸҗдҫӣ14дҪҚеҲҶиҫЁзҺҮпјҢдё”йҮҮз”Ё20MSPSгҖҒ40MSPSжҲ–65MSPSйҮҮж ·йҖҹзҺҮгҖӮе»әи®®еңЁ ADRF6510 е’Ң AD9248 зҡ„иҫ“еҮәд№Ӣй—ҙж”ҫзҪ®жҠ—ж··еҸ ж»ӨжіўеҷЁгҖӮжҠ—ж··еҸ ж»ӨжіўеҷЁи®ҫи®ЎзӨәдҫӢиҜ·еҸӮиҖғ ADRF6510 ж•°жҚ®жүӢеҶҢгҖӮ

ADRF6510 иҫ“еҮәе…ұжЁЎз”өеҺӢиҖғиҷ‘еӣ зҙ

ADRF6510 иҫ“еҮәе…ұжЁЎз”өеҺӢеҸҜеңЁ1.5VиҮі3.0VиҢғеӣҙеҶ…и°ғиҠӮпјҢдё”дёҚдјҡжҚҹеӨұй©ұеҠЁиғҪеҠӣгҖӮи®ёеӨҡзҺ°д»ЈADCзҡ„иҫ“е…Ҙе…ұжЁЎз”өеҺӢе°ҸдәҺ1.5VгҖӮе°ҶVOCMеј•и„ҡй©ұеҠЁиҮіе°ҸдәҺ1.5 Vзҡ„иҫ“еҮәе…ұжЁЎз”өеҺӢдҪҝ ADRF6510 зҡ„еӨұзңҹжҖ§иғҪејҖе§ӢдёӢйҷҚпјӣдҪҶеҷЁд»¶еңЁе°ҸдәҺ1.5 Vзҡ„е…ұжЁЎз”өе№ідёӢд»ҚеҸҜе·ҘдҪңгҖӮдёәдәҶдҝқжҢҒеӨұзңҹжҖ§иғҪпјҢеҸҜиғҪйңҖиҰҒзӣҙжөҒз”өе№іиҪ¬жҚўз”өи·ҜпјҢжҲ–иҖ…еҸҜдҪҝз”Ёе…·жңүиҫғдҪҺе…ұжЁЎз”өеҺӢзҡ„йӣҶжҲҗејҸж»ӨжіўеҷЁе’ҢVGAеҷЁд»¶пјҢдҫӢеҰӮADRF6516гҖӮ

з”өи·ҜиҜ„дј°дёҺжөӢиҜ•

йңҖиҰҒ/дҪҝз”Ёзҡ„и®ҫеӨҮ

дҝЎеҸ·еҸ‘з”ҹеҷЁеҢ…жӢ¬пјҡ

- Agilent E4438C vector signal generator

- AgilentE4438CзҹўйҮҸдҝЎеҸ·еҸ‘з”ҹеҷЁ

еҹәеёҰдҝЎеҸ·жҚ•иҺ·еҷЁд»¶жңү

- AgilentDSO90604AзӨәжіўеҷЁ

EVMиҝҗз®—еҷЁд»¶еҢ…жӢ¬пјҡ

- Agilent89600VSAиҪҜ件

- иҝҗиЎҢWindowsXPзҡ„PCпјҢйҖҡиҝҮUSBз”өзјҶиҝһжҺҘеҲ°зӨәжіўеҷЁ

з”өжәҗеҢ…жӢ¬пјҡ

- Вұ5Vз”өжәҗйҷӨ AD8130з”өи·ҜжқҝйңҖиҰҒВұ5VеӨ–пјҢжүҖжңүз”өи·ҜжқҝеқҮйңҖиҰҒ+5V

иҜ„дј°жқҝеҢ…жӢ¬пјҡ

- ADL5336-EVALZ (йңҖиҰҒдёҖдёӘ)

- ADL5387-EVALZ (йңҖиҰҒдёҖдёӘ)

- ADRF6510-EVALZ (йңҖиҰҒдёҖдёӘ)

- AD8130-EBZ (йңҖиҰҒдёӨдёӘ)

ејҖе§ӢдҪҝз”Ё

иҰҒдҪҝз”Ё ADL5336е’Ң ADRF6510пјҢйңҖиҰҒиҜ„дј°иҪҜ件жқҘжҺ§еҲ¶жҜҸдёӘеҷЁд»¶зҡ„еҗ„дёӘж–№йқўгҖӮжӯӨиҪҜ件еҸҜеңЁе·Ҙе…·гҖҒиҪҜ件е’Ңд»ҝзңҹжЁЎеһӢй“ҫжҺҘдёӯзҡ„еҗ„дёӘдә§е“ҒзҪ‘йЎөдёҠжүҫеҲ°гҖӮ

дёӢиҪҪе’Ңе®үиЈ…иҪҜ件еҗҺпјҢе°ҶUSBз”өзјҶд»Һз”өи„‘иҝһжҺҘеҲ°иҜ„дј°жқҝпјҢ然еҗҺй’ҲеҜ№йңҖиҰҒжҺ§еҲ¶зҡ„еҷЁд»¶иҝҗиЎҢиҪҜ件гҖӮ

еҠҹиғҪжЎҶеӣҫ

еӣҫ7жҳҫзӨәдәҶз”ЁдәҺжөӢиҜ•жҺҘ收й“ҫзҡ„жөӢиҜ•и®ҫзҪ®зҡ„еҠҹиғҪжЎҶеӣҫгҖӮ ADL5336иҜ„дј°жқҝд»…е…Ғи®ёеҚ•з«Ҝиҫ“е…Ҙе’Ңиҫ“еҮәгҖӮ ADL5387жқҝдёҠзҡ„RFиҫ“е…Ҙд№ҹжҳҜеҰӮжӯӨгҖӮзҹўйҮҸдҝЎеҸ·еҸ‘з”ҹеҷЁдёҠзҡ„RFиҫ“еҮәз«ҜеҸЈд»…дёәеҚ•з«Ҝпјӣеӣ жӯӨпјҢеҸ‘з”ҹеҷЁдёҺ ADL5336зҡ„иҫ“е…Ҙд№Ӣй—ҙйңҖиҰҒе·ҙдјҰгҖӮеҰӮеӣҫ7 жүҖзӨәпјҢзӣҙиҮі AD8130е·®еҠЁж”ҫеӨ§еҷЁзҡ„е…¶дҪҷдҝЎеҸ·и·Ҝеҫ„еқҮдёәе·®еҲҶгҖӮ з”ұдәҺзӨәжіўеҷЁд»…е…Ғи®ёеҜ№еҚ•з«ҜдҝЎеҸ·иҝӣиЎҢйҮҮж ·пјҢеҗҢж—¶еҸ—VSAиҪҜ件жҺ§еҲ¶пјҢеӣ жӯӨйңҖиҰҒе·®еҲҶиҪ¬еҚ•з«ҜиҪ¬жҚўгҖӮ

и®ҫзҪ®дёҺжөӢиҜ•

жҺҘ收жңәжөӢиҜ•и®ҫзҪ®зҡ„第дёҖжӯҘжҳҜејҖеҗҜжүҖжңүжөӢиҜ•и®ҫеӨҮгҖӮжөӢиҜ•и®ҫеӨҮйў„зғӯж—¶пјҢз”өи·Ҝжқҝеҝ…йЎ»жӯЈзЎ®й…ҚзҪ®д»ҘдҫҝеңЁдҝЎеҸ·й“ҫеҶ…жӯЈеёёдҪҝз”ЁгҖӮ

еңЁ ADL5336дёҠпјҢеә”зЎ®дҝқе®үиЈ…0wи·ізәҝз”өйҳ»пјҢе°ҶVGA1иҫ“еҮәиҝһжҺҘеҲ°VGA2иҫ“е…ҘгҖӮ

еңЁADL5387з”өи·ҜжқҝдёҠпјҢж—Ғи·Ҝиҫ“еҮәе·ҙдјҰд»ҘеңЁADL5387е’ҢADRF6510д№Ӣй—ҙжһ„е»әе®Ңж•ҙзҡ„е·®еҲҶгҖҒзӣҙжөҒиҖҰеҗҲдҝЎеҸ·и·Ҝеҫ„гҖӮ

еңЁ ADRF6510з”өи·ҜжқҝдёҠпјҢжү§иЎҢдёӢеҲ—ж“ҚдҪңпјҡ

- ж—Ғи·Ҝиҫ“е…Ҙе’Ңиҫ“еҮәе·ҙдјҰ

- еңЁиҫ“еҮәдҝЎеҸ·зәҝи·ҜдёҠж”ҫзҪ®1kе·®еҲҶиҫ“еҮәиҙҹиҪҪ(жҜҸдёӘиҫ“еҮәи·Ҝеҫ„дёҠж”ҫзҪ®дёӨдёӘжҺҘең°зҡ„500з”өйҳ»е°ұи¶іеӨҹдәҶ)

- з”Ё1ОјFз”өе®№еҸ–д»Јжҷ®йҖҡCOFSз”өе®№гҖӮ

еӣҫ7. жөӢиҜ•зӣҙжҺҘеҸҳйў‘жҺҘ收жңәзҡ„еҠҹиғҪжЎҶеӣҫ

收йӣҶиҜ„дј°жқҝ并е°ҶжүҖжңүдҝЎеҸ·и·Ҝеҫ„иҝһжҺҘеңЁдёҖиө·пјҢеҰӮеӣҫ7жүҖзӨәгҖӮе°ҶжүҖжңүз”өи·ҜжқҝиҝһжҺҘеҲ°+5VпјҢеҗҢж—¶е°ҶдёӨдёӘ AD8130жқҝиҝһжҺҘеҲ°-5VгҖӮиҜ·зЎ®дҝқз”өжәҗз”өжөҒдёҺжңҹжңӣеҖјдёҖиҮҙгҖӮ

еҰӮеӣҫ7жүҖзӨәпјҢе®ҢжҲҗдёӢеҲ—иҝһжҺҘпјҡ

- е°ҶзҹўйҮҸдҝЎеҸ·еҸ‘з”ҹеҷЁзҡ„еҚ•з«ҜгҖҒ50иҫ“еҮәиҝһжҺҘеҲ° ADL5336иҜ„дј°жқҝзҡ„INPUT1гҖӮ

- е°ҶAD8130зҡ„IдҝЎеҸ·и·Ҝеҫ„иҫ“еҮәиҝһжҺҘеҲ°зӨәжіўеҷЁдёҠзҡ„иҫ“е…Ҙ1пјҢ并е°ҶAD8130зҡ„QдҝЎеҸ·и·Ҝеҫ„иҫ“еҮәиҝһжҺҘеҲ°зӨәжіўеҷЁзҡ„иҫ“е…Ҙ3гҖӮ

- е°ҶUSBз”өзјҶд»ҺPCиҝһжҺҘеҲ°зӨәжіўеҷЁгҖӮ

- е°ҶдҝЎеҸ·еҸ‘з”ҹеҷЁзҡ„RFз«ҜеҸЈиҝһжҺҘеҲ°ADL5387иҜ„дј°жқҝзҡ„LOиҫ“е…ҘгҖӮ

еңЁAgilentE4438CдҝЎеҸ·еҸ‘з”ҹеҷЁдёҠпјҢжү§иЎҢдёӢеҲ—ж“ҚдҪңпјҡ

- е°Ҷйў‘зҺҮи®ҫзҪ®дёә400MHz

- е°Ҷе№…еәҰи®ҫзҪ®дёә0dBm

- жҺҘйҖҡRFз«ҜеҸЈ

еңЁAgilentE4438CзҹўйҮҸдҝЎеҸ·еҸ‘з”ҹеҷЁдёҠпјҢжү§иЎҢдёӢеҲ—ж“ҚдҪңпјҡ

- е°ҶRFиҪҪжіўйў‘зҺҮи®ҫзҪ®дёә200MHz

- жҺҘйҖҡRFз«ҜеҸЈ

- жҺҘйҖҡRFз«ҜеҸЈ

- жҺҘйҖҡзҹўйҮҸдҝЎеҸ·еҸ‘з”ҹеҷЁеҶ…йғЁзҡ„е®ҡеҲ¶ARB

- е°ҶдҝЎеҸ·и®ҫзҪ®дёә4-QAMпјҢз¬ҰеҸ·йҖҹзҺҮи®ҫзҪ®дёә5MSPSпјҢи„үеҶІж•ҙеҪўж»ӨжіўеҷЁеҖји®ҫзҪ®дёә0.35

еңЁPCдёҠпјҢеҗҜеҠЁAgilent89600VSAиҪҜ件гҖӮеңЁVSAиҪҜ件дёӯпјҢжү§иЎҢдёӢеҲ—ж“ҚдҪңпјҡ

- жҺҘйҖҡж•°еӯ—и§Ји°ғеҷЁ

- е°Ҷиҫ“е…Ҙи®ҫзҪ®дёәI+jQйҖүйЎ№

- е°Ҷйў‘зҺҮи®ҫзҪ®дёә0HzпјҢз¬ҰеҸ·йҖҹзҺҮи®ҫзҪ®дёә5MSPSпјҢеҖји®ҫзҪ®дёә0.35

зҹўйҮҸдҝЎеҸ·еҸ‘з”ҹеҷЁдёҠзҡ„дҝЎеҸ·жҢҮж Үеҝ…йЎ»еҢ№й…ҚVSAиҪҜ件дёҠзҡ„жҢҮж ҮгҖӮиҪҜ件еҗҜеҠЁеҗҺпјҢеә”жҳҫзӨәIQжҳҹеә§еӣҫзӘ—ж је’Ңйў‘и°ұзӘ—ж јгҖӮеңЁVSAиҪҜ件дёӯйҖҡиҝҮдёӢеҲ—жӯҘйӘӨж·»еҠ дҝЎжҒҜзӘ—еҸЈпјҡ

1. зӮ№еҮ»жҳҫзӨә

2. зӮ№еҮ»еёғеұҖ

3. йҖүжӢ©ж …ж ј2Г—2

й»ҳи®Өжғ…еҶөдёӢпјҢе·Із»ҸжҳҫзӨәзҡ„е…¶д»–дёӨдёӘзӘ—ж јеә”дёәиҜҜе·®зҹўйҮҸдёҺж—¶й—ҙе’ҢдҝЎжҒҜзӘ—еҸЈпјҡз¬ҰеҸ·/иҜҜе·®гҖӮеҰӮжһң并йқһеҰӮжӯӨпјҢжү§иЎҢдёӢеҲ—ж“ҚдҪң

1. еҸҢеҮ»д»»ж„ҸзӘ—ж јзҡ„ж Үйўҳ

2. еңЁеҮәзҺ°зҡ„зӘ—еҸЈдёӯйҖүжӢ©з¬ҰеҸ·/иҜҜе·®

з¬ҰеҸ·/иҜҜе·®зӘ—ж јжҸҗдҫӣи®ёеӨҡз»“жһңпјҢеҢ…жӢ¬EVMгҖӮиҪҜ件еә”й”Ғе®ҡеңЁдҝЎеҸ·дёҠпјҢ并жҠҘе‘ҠEVMж•°еҖјгҖӮ

AGCи®ҫе®ҡзӮ№гҖҒжңҖеӨ§еўһзӣҠе’Ңж»ӨжіўеҷЁеёҰе®Ҫе…ЁйғЁеҸҜйҮҮз”ЁдёӘеҲ«еҷЁд»¶зҡ„еҗ„жҺ§еҲ¶иҪҜ件жқҘи®ҫзҪ®гҖӮ ADL5336иҫ“е…Ҙз«Ҝзҡ„еҠҹзҺҮжҺ§еҲ¶еҸҜйҖҡиҝҮзҹўйҮҸдҝЎеҸ·еҲҶжһҗд»ӘдёҠзҡ„еҠҹзҺҮжү«жҸҸе®ҢжҲҗгҖӮд»Һ−80dBmжү«жҸҸиҮіеҮ д№Һ+16dBmпјҢд»ҘдҫҝеңЁжӯӨжөӢиҜ•и®ҫзҪ®дёӢжөӢиҜ•жҺҘ收жңәгҖӮ ADRF6510дёҠзҡ„еўһзӣҠе§Ӣз»Ҳи®ҫзҪ®дёәе®һзҺ°1.5Vp-pе·®еҲҶиҫ“еҮәз”өе№іпјҢеҒҮе®ҡжңүи¶іеӨҹзҡ„еўһзӣҠеҸҜз”ЁгҖӮжҹҗдәӣжғ…еҶөдёӢпјҢеҜ№дәҺжһҒе°Ҹзҡ„дҝЎеҸ·з”өе№іпјҢ ADRF6510ж— и¶іеӨҹзҡ„еўһзӣҠжқҘеҲ°иҫҫ1.5Vp-pе·®еҲҶз”өе№ігҖӮ

CIRCUITS FROM THE LABе®һйӘҢе®Өз”өи·Ҝ

- з»ҸиҝҮжһ„е»әе’ҢжөӢиҜ•еҸҜд»ҘзЎ®дҝқеҠҹиғҪе’ҢжҖ§иғҪзҡ„з”өи·Ҝи®ҫи®ЎгҖӮ

- еҖҹеҠ©ADIе…¬еҸёдј—еӨҡеә”з”Ёдё“дёҡжҠҖжңҜпјҢи§ЈеҶідәҶеӨҡз§Қеёёи§Ғзҡ„жЁЎжӢҹгҖҒRF/IFе’Ңж··еҗҲдҝЎеҸ·и®ҫи®ЎжҢ‘жҲҳгҖӮ

- й…Қжңүе®ҢеӨҮзҡ„ж–ҮжЎЈпјҢжҳ“дәҺеӯҰд№ гҖҒзҗҶи§Је’ҢйӣҶжҲҗгҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·