在深入分析噪声问题的基础上,提出一种共基差分输入结构设计低噪声放大器的电路结构,电路中包括可控增益放大器和增益控制电路。

低噪声放大器的输出电压直接反映到自动增益控制电路的输入端,根据输出电压幅值的大小,自动增益控制电路的输出电压反馈到低噪声放大器的增益控制电路比较器的输入端,进而影响放大器的总体增益。基于JAZZ O.35 μmBICMOS工艺设计放大器电路,这种结构的电路具有低噪声高增益的特点。

1 低噪声放大器设计中的噪声问题

最常见的噪声源是平带(Flatband)噪声,也称白噪声。平带噪声源产生散粒噪声和热噪声。散粒噪声是由电子通过一个势垒的离散量子性质产生的,通常与二极管和双极晶体管有关。散粒噪声的产生必须具备两个条件:直流电流的存在以及带电载流子必需越过势垒以产生电流。散粒噪声计算公式:

式中,q为电子电荷,ID为正向结电流,△f是单位频率的噪声频宽。

可以看出,散粒噪声与结电流的平方根成正比,与频率大小和温度无关。将散粒噪声电流乘以动态结阻抗,可将散粒噪声表达为噪声电压。

热噪声是由器件内的载流子随机运动产生的。任何元器件,只要有直流电阻,就存在热噪声(交流电阻是一个等效的概念,不单独产生热噪声)。由于噪声过程是随机的,它的幅值符合高斯分布,表征热噪声通常的方法就是测量其产生噪声的器件的平均噪声功率。

其噪声功率公式如下:

式中,K为波尔兹曼常数,K=1.38x10-23J/K,T为绝对温度,△f是单位频率的噪声频宽。因此,热噪声与频率大小无关。

电阻的热电压是电阻、温度和测量带宽的函数:

式中,En为在给定温度下电阻R在带宽△f上电路产生的RMS(均方根)噪声电压。

式(3)两边除以电阻值后即得诺顿等效噪声源:

按1 Hz带宽对RMS噪声电压和噪声电流进行归一化,即可得到频谱密度:

与散粒噪声电流的情况一样,如果信号幅度增大比噪声更快,则可通过增加噪声的绝对幅度来提高电路的性能。

2 低噪声放大器的设计

2.1 低噪声放大器电路的结构设计

两种常见的低噪声放大器分别为:双极型输入和CMOS输入。传统上,CMOS放大器以低输入偏置电流而闻名,却总是受高电压噪声所累。典型的CMOS放大器的平带噪声为几十nV/Hz,1/f噪声的峰至峰值范围为几微伏。双极型放大器本身噪声较低,是低噪声应用的最常见选择。

在射频范围内,MOS管的主要噪声源为沟道热噪声、栅感应噪声与栅分布电阻热噪声。由于MOS晶体管的沟道电阻产生比较大的热噪声,所以选择双极输入会得到一个相对较好的噪声系数。低噪声双极型放大器,可提供极低的输入电压噪声密度和相对较高的输入电流噪声密度。

单端LNA结构对于接地的寄生电感非常灵敏。差分结构由于对称点上的增量(交流)接地,不会受到电流源接地回路中寄生参数的影响。差分结构的另一个重要优点是它有抑制共模干扰的能力。这一考虑在混合信号应用中特别重要,因为无论是电源电压还是衬底电压都可能含有噪声。为使在高频时的共模抑制比最大,关键是绝对要使版图尽可能地对称。差分结构的放大器对抑制噪声也有显著的作用。双极型LNA共基极结构相对于共射极电路具有三个显著的优点:更为简单的输入匹配、更高的线性度和更大的逆向隔离,所以电路采用共基极输入。

2.2 低噪声放大器的电路设计

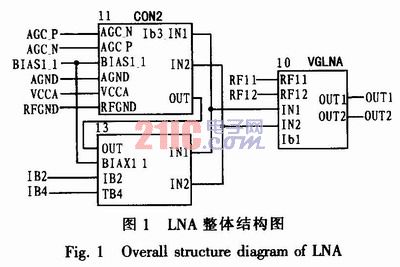

低噪声放大器整体结构如图1所示,电路分为3部分,其中模块VGLNA是可控增益放大器,这部分的增益可以改变。模块CON1和CON2为增益控制电路,通过AGC的控制电压来调整VGLNA的增益。对模块VGLNA的设计目标是使增益达到25 dB以上。模块CON1和CON2的设计目标是通过改变节点IN1、IN2电压值,使VGLNA的增益变化不超出AGC的动态范围。

2.2.1 可变增益放大器的设计

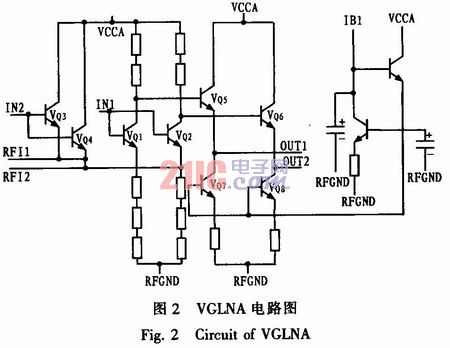

可变增益放大器的电路如图2所示,模块VGLNA采用两级放大,整个电路的增益主要来自第一级由VQ1、VQ2组成的共基放大器,射频信号RFI1和 RFI2分别由VQ1和VQ2的射极输入。第二级为射随放大器电路,具有高输入电阻、低输出电阻和近似为单位1的电压增益,对总体增益基本没有贡献。

设连接VQ1、VQ2集电极的串联电阻为RC,连接VQ1、VQ2发射极的串联电阻为RE。RE用来设置合适的工作点,而RC则是把输出电流转换为电压。室温下,VQ1、VQ2的单管增益为:

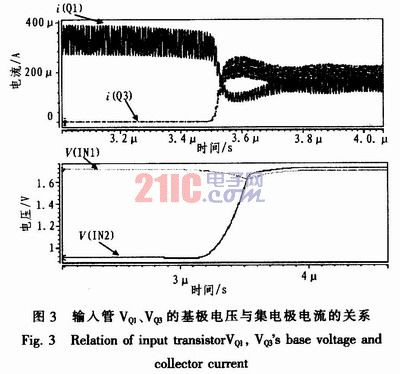

输入管VQ1、VQ3的基极电压与集电极电流的关系如图3所示,可以看出基极电压与电流的关系。假设VQ3、VQ4不工作,即VIN2的电压值小于0.9 V。若流过VQ1的电流Ic为340 μA,Rc为2 kΩ。则Av=24,即VQ1,VQ2的单管增益为27 dB。

RFI1、RFI2输入信号的工作点电压为:

![]()

VQ3、VQ4管的作用是通过分流减小VQ1、VQ2管的增益。升高IN2点的电压可使VQ3、VQ4管导通。改变VIN1,VIN2的电压值,使流过 VQ1的电流减小,流过VQ3的电流增大,VQ1管增益减小。为满足增益变化,且输出不大于100 mV的限制,要求控制电压VIN1的变化范围为1.7l~1.69 V,VIN2的范围为0.9~1.71 V。

2.2.2 增益控制级的设计

模块CON2是一个比较器电路,通过改变输入VAGC_N和VAGC_P的电压值,对VIN1和VIN2进行控制。根据VGLNA的目标要求,VIN1的变化范围为1.7l~1.69 V,VIN2的范围为0.9~1.71 V,模块CON2的输出要达到这个要求。

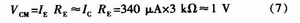

2.2.3 增益控制级CON1的设计

模块CON1的作用是对VIN1和VIN2的值进行反馈控制。CON1的电路如图4所示,IN1,IN2作为模块CON1比较器的一个输入电压VN,与另一端的基准电压VR进行比较。假设VIN2=0.9 V,即VQ2管不工作,同时模块CON2的VQ12管也不工作。由于节点IN1的电平VIN1较低,导致VN>V R,I1<I2,且I1=I3,则I2>I3,要从CON2的比较器的节点OUT中抽取一部分电流Io,等效于CON2的比较器多了一个电流源。这样流过VQ11一路的电流增大,VIN1也增大。VIN1反馈到CON1的VQ1管,使VN逐渐接近基准电压VR。当VN=VR时,I1=I2,则 I3=0,这时CON1对CON2没有控制作用,流过VQ1、VQ2的总电流达到了一个恒定的值。

3 电路仿真结果与分析

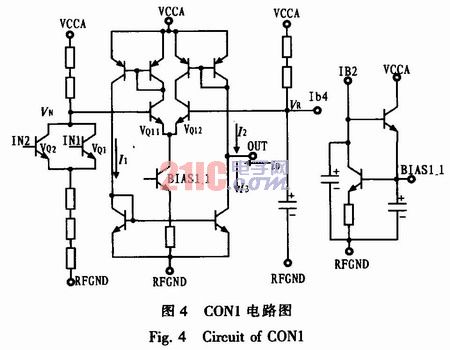

根据前文分析,这里只考虑热噪声。VGLNA的小信号模型如图5所示。

LNA包括两级放大器,第2级的射随放大器输出电阻Ro为

将式(9)、(10)和(11)带入式(12),可得到输出热噪声谱密度为:

![]()

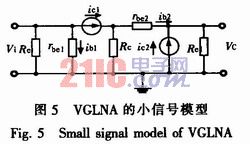

则总输出电压噪声的均方根值约为![]() 。以上的结论都是在假设噪声是不相关的条件下得出的。噪声波形曲线如图6所示,实际仿真结果与计算所得的结果相符。

。以上的结论都是在假设噪声是不相关的条件下得出的。噪声波形曲线如图6所示,实际仿真结果与计算所得的结果相符。

噪声系数为输入信噪比除以输出信噪比,公式为NF=(SI/NI)/(So/No)。输入信噪比约为2μV/139 pV=1.44x104,输出信噪比为44μV /2.7 nV=1.6x104。所以噪声系数NF=1.44/1.6=0.9<1 dB。

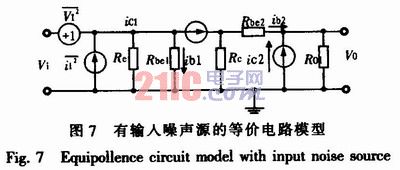

输入等价噪声模型如图7所示,电路的等价输入噪声为输出噪声除以增益,所以:

![]()

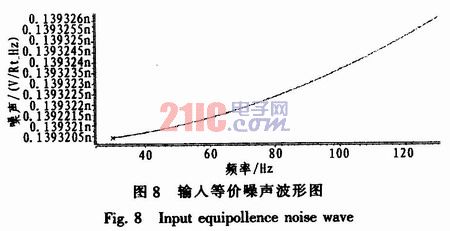

仿真结果如图8所示,输入等价噪声约为![]() ,与理论计算基本相符。

,与理论计算基本相符。

输入信噪比约为2 μV/139 pV=1.44x104,输出信噪比为44μV/2.7 nV=1.6x104,噪声系数NF=1.44/1.6=0.9<1 dB。

4 结论

本设计基于JAZZ 0.35 μm BICMOS工艺设计了一种低噪声放大器。通过理论分析和仿真结果表明,设计采用的共基极输入和射极跟随器的结构可以有效地抑制噪声。该低噪声放大器能提供25 dB的增益,噪声系数小于1 dB,灵敏度达到2 μV,达到无线调频接收机中低噪声放大器的电路设计要求。

粤公网安备 44030902003195号

粤公网安备 44030902003195号