随着半导体制造能力允许在单块芯片上集成数千门逻辑电路,系统级芯片(SoC)开始占据未来IC技术的中心。不过,当今天人们在谈论SoC时,他们实际谈论的只是部分系统——仅是把数字基带与数据转换器、一些高速模拟IO、甚至一些射频电路集成在一起,只要它不会太复杂。

由于工艺技术的不兼容性,RF集成通常被认为是一种基本上尚未解决的SoC挑战。在数字裸片上集成RF电路会限制良品率或导致高昂的测试成本,从而极大地增加生产成本。

但问题比这更复杂和微妙。从SoC系统层面上来看,RF集成将给硬件器件的电路设计、物理实现及制造与测试带来一些困难的开发挑战。

现在,RF芯片设计者有了另一种选择。CMOS制造工艺技术的最新发展克服了RF集成障碍,使开发者可以将RF处理移到数字域中。芯片设计者不必费劲去设计和实现模拟器件,相反,他们可以采用数字RF技术,并利用熟悉的工具和工艺来处理RF信号。

不可能只集成一种无线电

为了适应手机或PDA的小外形尺寸,这要求在一块芯片上同时集成数字、模拟及RF,否则成本与外形尺寸限制将阻碍手机配置新的功能。集成的无线电只有传统无线电一半的硅面积,占有一半的板空间,消耗大约一半的功率。因此,无线电集成在满足手机设计目标方面提供了极大的优势。

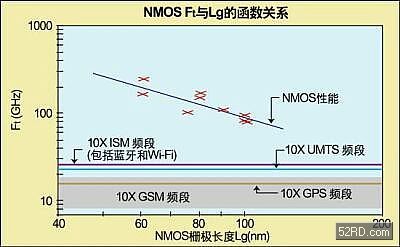

图1:跟踪每个工艺节点的截止频率可以评估哪

些通信频段能够在数字域中进行处理。

让我们来看看3G手机的数据处理要求。在数字域,用户希望拥有更高分辨率的彩屏显示器、需要额外存储器与图形资源的游戏、PDA应用功能以及诸如照相、视频会议及音频播放等多媒体功能。在RF方面,一部手机集成好几种无线电并非是不合理的,它们包括:

* 很多GSM手机都支持全部四个频段——欧洲的蜂窝与DCS以及美国的不同蜂窝频率与PCS

* 2.1 GHz的UMTS

* 用于定位与同步的GPS

* 用于PAN连接的蓝牙

* 用于网络连接的WiFi,如果是2.4 GHz 802.11b/g,则可共用蓝牙无线电

* 数字电视(DTV)

* 数字音频广播与调频广播等

今天,板上的RF器件数已超过总器件数的一半,而且一种简单的无线电就要占去手机印制电路板(PCB)40%的面积。如果靠增加无线电来支持蓝牙、GPS及WLAN等功能,那么会显著增大这些数字。尽管无线电能共用一些电路,但如果它们想要装入一部设备中,则必须比它们今天的尺寸小。

存在的问题

集成数字、模拟及RF电路所遭遇的实际问题向那些对整体硅集成充满热情的人泼了一盆冷水。对于在SoC上集成复杂RF电路的设计来说,可用的EDA开发工具仍存在许多有待改进之处。

用于同时验证数字与RF电路的工具仍处于发展的初期阶段,更谈不上同时对设计进行验证与测试。其他局限还包括小器件的不良匹配、高1/f噪声、以及缺少带足够模拟特征的片上无源器件(电阻、电容及变容二极管)等。

尽管存在这些挑战,集成仍然是使智能电话降低无线电设计的成本、功耗及复杂性的基本手段。为了使无线电集成成为现实,业界要求在晶圆工艺、系统设计及电路设计层面上有显著的技术进步。尽管采用SoC的设计者并不关心许多SoC技术挑战,但了解这些挑战也很重要,因为它们决定了实际器件的能力与局限。例如,尽管使用双极或BiCMOS工艺集成RF在技术上是可行的,但测试器件时的良率限制及高昂成本使得这些器件未必能实现大批量或商业生产。

集成硅锗(SiGe) BiCMOS技术也是可能的做法。但硅锗技术一般比先进的数字CMOS工艺落后1个或2个工艺节点。由于手机需要越来越多的处理资源,硅锗工艺无法使数字部分(特别是存储器)的裸片成本保持最低。

即使CMOS RF集成也有它的挑战。模拟混频器、滤波器及放大器等的实现都很困难,尤其随着电压下降,新工艺节点早期的器件建模一般都不足以达到模拟模块设计所需的高精度参数建模。业界要求有重大的设计创新,从而允许无线电被集成在标准的CMOS中,并充分利用CMOS技术的优势。

数字RF集成解决RF集成问题的一种不同方法是完全避免它们,这可通过将RF器件的功能转换到数字域来实现。

通过在CMOS数字域处理RF信号,就没有必要使用复杂且昂贵的模拟掩模。芯片设计也变得更加容易,因为开发者在仿真时可以更容易了解系统细节,并能通过整合可编程软硬件元素来执行处理,从而增强对信号处理过程的控制。

例如,从电源耦合到发射与接收压控振荡器(VCO)上的噪声会影响整体系统效率。因此,大多数无线电路板设计都要求使用调节器及相关无源器件来解决此问题。将这些器件集成在无线电收发器中,意味着简单的去耦电容是所需的、要求与电池直接相连的唯一外部元件,从而可简化设计并节省板空间。

设计者还可选择将数字调谐及自校准功能集成到VCO中,并通过集成环路滤波器来扩大VCO的调谐范围。

为使数字电路能处理模拟信号,它们必须工作在极高的速度。器件截止频率(Ft)是一种用来评价工艺处理RF信号能力的简单方法(参见图1)。

总的原则是,Ft应大约为工作频率的10倍。例如,要处理1.9 GHz的信号,Ft就必须大约为19 GHz。缺少足够的Ft是老式CMOS工艺的一个主要局限,但今天的90纳米技术可提供超过100 GHz的Ft性能。这种极高的Ft很容易就超过蜂窝手机无线电的所有要求。

数字RF处理在过去十年间已经登上历史舞台,但随着SoC转向90纳米工艺,“高频”的含义将随着Ft的提高而被重新定义。今天,运行在1 GHz的DSP能处理整个数字域中的“高频”信号,甚至可用软件来动态控制信号处理。

最近,TI公布了第二代蓝牙SoC 芯片——BRF 6150,这款芯片给出了用CMOS工艺进行SoC集成如何能简化设计并降低板空间要求和系统成本的一个范例。BRF6150在一个4.5mm x 4.5mm的封装内集成了蓝牙基带、数字RF及天线开关,使设计者能在50平方毫米的面积内增加蓝牙功能(见图2)。

集成式BRF6150的功耗比同类解决方案低30%,且其待机电流仅为6uA。它直接与电池连接,无需使用外部调节器。该芯片仅需11个外部器件,从而简化了设计复杂性。这种集成式蓝牙芯片是提高集成度和转向真正数字无线电的典型成果。

蓝牙之外

今天,我们能集成蓝牙的一个主要原因是,它采用功率相对较低、仅需短距离传输的信号。现代手机要求有-106dBm量级的灵敏度,且必须能对邻近频段有60dB的抑制,并采用可避免将相位噪声引入接收频段的振荡器。这些极端的性能要求使无线电集成具有更大的挑战。使设计者可以满足这些苛刻设计约束的许多关键器件,已经能够在数字域中找到解决方案。例如,全集成的数字频率合成器已经面市,它的所有内部元件都在片上而且没有外部引脚,这是RF集成技术的一个重要里程碑。

集成的另一个关键优势是,通过使用更小尺寸的工艺技术进行设计,无线电能工作在更低的电压上。在大多数情况下,在较低的电压上工作绝对是一个优势,因为能获得更长的电池使用寿命(这是在现有手机上引入新功能的一个主要障碍)以及具有更小的散热。

但低电压同时也会带来一些基本问题,如动态范围。动态范围挑战会因为无线通信的远近而显现出来。例如,如果手机A靠近蜂窝而手机B远离蜂窝,则手机B就必须在最大功率上发射信号,才能连接蜂窝。

当信道A和信道B处于不同频率上时,信道B的高功率信号有可能泄漏至信道A中,故要求手机A具有抑制远信道干扰的能力,以便能在有高功率发射存在的情况下接收微伏信号。幸运的是,像动态范围这些问题可通过前端处理这种直接的方式来加以解决。

产生适合用来驱动天线的高功率信号是SoC集成面临的另一个关键挑战。通常,广域网(WLAN)所用功放的高功率、高电压及高散热等因素,使它们不适合用深亚微米CMOS工艺来进行集成。

但需指出的是,这些问题主要与现有广域网(如GSM 及CDMA)有关,而距离较短的个人区域网(PAN)以及局域网(LAN)可以采用功放集成。

在这种SoC设计中,将功放靠近数据处理器放置可执行自动系统校准,从而提高整体系统性能。此外,由于通过RF集成可以节省成本、板空间及功耗,数字RF还能加快一些新兴短距离网络(包括UWB、Zigbee及网格网络等)的开发。

批量验证

模拟RF集成的另一个主要障碍是验证,这甚至比保持手机所要求的大批量生产的良品率更令人生畏。生产用RF测试仪通常不能测试数字逻辑阵列,而逻辑测试仪又不能提供模拟或RF测试能力。但我们既不能让大型SoC的RF部分对良品率产生很大的影响,也不能让它延缓SoC向最新工艺节点的移植。

通过将RF功能移到数字域,数字RF处理使得测试和验证无线电的过程接近于只有逻辑电路的情况。尽管永远都不可能实现完全的移植(总是存在一定的模拟与混合信号功能),但数字处理技术可用来提高测试与验证过程的效率及可靠性。

采用数字RF,我们可以完全分析在SoC上的基带信号特征,而且一些外部模拟器件也可以实现闭环测试,以评估信号质量。采用这种方式,我们能够在系统级,而不只是在功能模块级上对无线电性能进行测量。

这不仅能减少所需测量的数量,而且能简化验证过程。SoC可带有自检测能力,以执行自校准并减少参数变化对良品率的影响。这能将良品率维持在缺陷密度限制以内,并将无线电测试成本降低至一个很低的水平。此外,数字RF模块还能保持进行工艺移植的能力,从而可对芯片进行缩放,这也是大批量器件生产的一个重要要求。

在数字域实现RF功能还能通过执行系统级优化来减少器件成本及复杂性。例如,处理来自多个无线电的很多频率,不只是要求将多个无线电放在同一块裸片上。通过系统级设计,设计者可采用适当的电路来减少带内寄生信号的产生。设计者还能开发新的架构,以实现硬件共用(例如两个无线电共用一个功能块等),从而进一步减小无线电尺寸。由于这些新架构主要是以数字逻辑实现,所以设计者可采用熟悉的EDA仿真与综合工具,以及数字测试与制造测试套件。

RF无疑是SoC集成的下一个主要挑战,但随着CMOS工艺等制造技术的进一步发展,RF处理已开始转变成数字域中的设计问题。

随着每个工艺节点的尺寸减小及晶体管速度的提高,数字RF处理将能适用于越来越多的通信频段。RF集成不再是一个是否可行的问题,而且SoC芯片最终能变成在单个芯片上真正完整的系统。

作者:Bill Krenik

无线高级架构经理

TI公司

Gene Frantz

美国数字信号处理专家

粤公网安备 44030902003195号

粤公网安备 44030902003195号