ж·ұе…ҘдәҶи§Јжү«жҸҸйҳөеҲ—йӣ·иҫҫдҝЎеҸ·еӨ„зҗҶ

дё»еҠЁз”өжү«жҸҸйҳөеҲ— (AESA) йӣ·иҫҫжҳҜеҪ“д»Ҡе…ҲиҝӣжӯҰеҷЁзі»з»ҹзҡ„е…ій”®з»„жҲҗ пјҢ зү№еҲ«жҳҜжңәиҪҪдҪңжҲҳзі»з»ҹгҖӮиҖҢе…¶дҪ“зі»з»“жһ„зҡ„жңӘжқҘеҸ‘еұ•е°Ҷи¶…и¶ҠжңҖеҲқзҡ„еҶӣдәӢеә”з”ЁпјҢ延伸еҲ°ең°зҗғзү©зҗҶжөӢз»ҳгҖҒжұҪиҪҰиҫ…еҠ©й©ҫ驶гҖҒиҮӘеҠЁиҪҰиҫҶгҖҒе·ҘдёҡжңәеҷЁдәәе’ҢеўһејәзҺ°е®һзӯүйўҶеҹҹпјҡе®һйҷ…дёҠпјҢиҝҷеҢ…жӢ¬д»»дҪ•йңҖиҰҒеҜ№еӨ§йҮҸзҡ„дј ж„ҹеҷЁж•°жҚ®иҝӣиЎҢи°ғзҗҶпјҢиһҚеҗҲеҲ°жЁЎеһӢдёӯиҝӣиЎҢеҲӨеҶізҡ„еә”з”ЁгҖӮ

е…ёеһӢзі»з»ҹзҡ„и§’иүІ

иҝҷдёҖж–№жі•йҒҝе…ҚдәҶйҮҮз”ЁеӨ§йҮҸзҡ„移еҠЁйғЁд»¶пјҢж”ҜжҢҒйӣ·иҫҫе®һзҺ°дј з»ҹеӨ©зәҝйҮҮз”Ёзү©зҗҶж–№жі•ж— жі•иҺ·еҫ—зҡ„еҠҹиғҪпјҢдҫӢеҰӮпјҢзһ¬ж—¶ж”№еҸҳжіўжқҹж–№еҗ‘пјҢеҸ‘йҖҒе’ҢжҺҘ收еҗҢж—¶жңүеӨҡдёӘеӨ©зәҝж–№еҗ‘еӣҫпјҢжҲ–иҖ…жҠҠйҳөеҲ—еҲҶжҲҗеӨҡдёӘеӨ©зәҝйҳөпјҢе®ҢжҲҗеӨҡйЎ№еҠҹиғҪ —— д№ҹе°ұжҳҜпјҢж №жҚ®ең°еҪўжҗңзҙўзӣ®ж ҮпјҢеҗҢж—¶и·ҹиёӘзӣ®ж ҮгҖӮиҝҷдәӣж–№жі•еҸӘйңҖиҰҒеңЁеҸ‘йҖҒеҷЁеўһеҠ дёҖдәӣдҝЎеҸ·пјҢеңЁжҜҸдёҖжҺҘ收еҷЁе°ҶдҝЎеҸ·еҲҶејҖгҖӮйҮҚеҸ жҳҜдёҖз§ҚеҫҲеҘҪзҡ„ж–№жі•гҖӮ

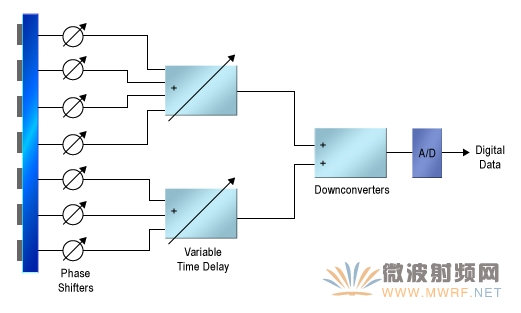

дёҖдёӘе®Ңж•ҙзҡ„зі»з»ҹд»ҺCPUз°Үдј иҫ“еҲ°еӨ©зәҝпјҢ然еҗҺеҶҚиҝ”еӣһ ( еӣҫ 1 ) гҖӮ дёҖејҖе§ӢеӨ„зҗҶж—¶пјҢиҪҜ件жҺ§еҲ¶зҡ„жіўеҪўеҸ‘з”ҹеҷЁдә§з”ҹзі»з»ҹиҰҒеҸ‘йҖҒзҡ„е•Ғе•ҫгҖӮеҸ–еҶідәҺеә”з”ЁпјҢйҷҚеҷӘгҖҒеӨҡжҷ®еӢ’еӨ„зҗҶе’Ңйҡҗиә«зҡ„йңҖжұӮдјҡеҜ№дҝЎеҸ·жңүжүҖжҚҹдјӨгҖӮ

еӣҫ 1 .дёҖдёӘйқһеёёз®ҖеҢ–зҡ„ AESA зі»з»ҹз»“жһ„еӣҫгҖӮ

дёҖејҖе§ӢпјҢжҺҘ收еҲ°зҡ„дҝЎеҸ·е®һйҷ…дёҠйҖҡиҝҮдёҺеҸҚж–№еҗ‘зӣёеҗҢзҡ„йҖҡи·ҜпјҢеңЁеҗҺз«ҜиҰҒиҝӣиЎҢжӣҙеӨҡзҡ„еӨ„зҗҶгҖӮеңЁжҜҸдёҖдёӘеӨ©зәҝеҚ•е…ғпјҢйҷҗе№…еҷЁе’ҢеёҰйҖҡж»ӨжіўеҷЁдҝқжҠӨдәҶдҪҺеҷӘеЈ°ж”ҫеӨ§еҷЁгҖӮж”ҫеӨ§еҷЁй©ұеҠЁ RF дёӢеҸҳйў‘еҷЁпјҢеҸҜд»Ҙз»“еҗҲжЁЎжӢҹж”ҫеӨ§е’Ңи°ғзӣёеҠҹиғҪгҖӮдҝЎеҸ·д»Һ IF зә§дј иҫ“еҲ°еҹәеёҰпјҢжҜҸдёҖеӨ©зәҝеҚ•е…ғзҡ„дҝЎеҸ·еҲ°иҫҫе…¶жЁЎж•°иҪ¬жҚўеҷЁ (ADC) гҖӮ然еҗҺпјҢиҒҡжқҹжЁЎеқ—жҠҠеӨ©зәҝдҝЎеҸ·йҮҚж–°з»„еҗҲжҲҗдёҖи·ҜжҲ–иҖ…еӨҡи·ҜеӨҚж•°ж•°жҚ®йҮҮж ·жөҒпјҢжҜҸдёҖж•°жҚ®жөҒд»ЈиЎЁдәҶжқҘиҮӘжҹҗдёҖжҺҘ收波жқҹзҡ„дҝЎеҸ·гҖӮиҝҷдәӣдҝЎеҸ·жөҒйҖҡиҝҮеӨ§еҚ з©әжҜ”зҡ„ж•°еӯ—дҝЎеҸ·еӨ„зҗҶ (DSP) з”өи·ҜпјҢиҝӣдёҖжӯҘи°ғзҗҶж•°жҚ®пјҢиҝӣиЎҢеӨҡжҷ®еӢ’еӨ„зҗҶпјҢе°қиҜ•д»ҺеҷӘеЈ°дёӯжҸҗеҸ–еҮәе®һйҷ…дҝЎеҸ·гҖӮ

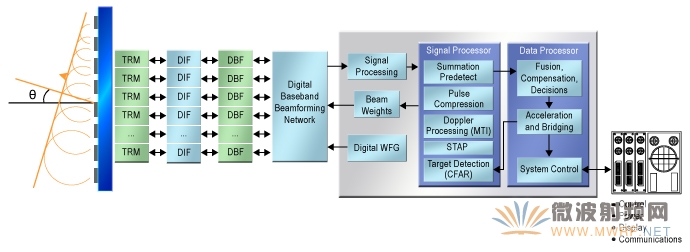

д»Җд№Ҳж—¶еҖҷиҝӣиЎҢж•°жҚ®иҪ¬жҚў

зӣ®еүҚеҸҜд»ҘжҠҠж•°жҚ®иҪ¬жҚўеҷЁж”ҫеңЁ IF дёӯпјҢиҝӣиЎҢ IF йў‘зҺҮиҪ¬жҚўпјҢжүҖжңүеҹәеёҰеӨ„зҗҶе·ҘдҪңйғҪжҳҜж•°еӯ—еҢ–зҡ„ ( еӣҫ 2 ) гҖӮ еҸҜд»ҘеңЁеҹәеёҰиҒҡжқҹзҪ‘з»ңдёӯпјҢд»Ҙж•°еӯ—ж–№ејҸеңЁеӨ©зәҝеҚ•е…ғд№Ӣй—ҙдә§з”ҹе№Іж¶үж–№еҗ‘еӣҫзҡ„时延пјҢжҜҸдёҖдёӘеӨ©зәҝеҚ•е…ғ并дёҚйңҖиҰҒжЁЎжӢҹзӣёз§»еҷЁжҲ–иҖ…延时зәҝгҖӮиҝҷз§ҚеҲ’еҲҶж–№жі•ж”ҜжҢҒ DSP и®ҫи®Ўдәәе‘ҳжҠҠеҸ‘йҖҒе’ҢжҺҘ收йҖҡи·ҜеҲҶи§ЈжҲҗеҲҶз«Ӣзҡ„еҠҹиғҪ —— д№ҳжі•еҷЁгҖҒж»ӨжіўеҷЁгҖҒз”ЁдәҺ延时зҡ„ FIFO пјҢд»ҘеҸҠеҠ жі•еҷЁпјҢеңЁ MATLAB дёӯеҜ№е…¶иҝӣиЎҢе»әжЁЎпјҢд»Һеә“дёӯе®һзҺ°е®ғ们гҖӮеҸҜд»ҘжҠҠиҰҒжұӮжңҖиӢӣеҲ»зҡ„еҠҹиғҪж”ҫеҲ°дё“й—ЁејҖеҸ‘зҡ„ ASIC гҖҒ FPGA жҲ–иҖ… GPU иҠҜзүҮдёӯпјҢиҖҢжҠҠиҰҒжұӮдёҚеӨӘй«ҳзҡ„иҝҗз®—еҲҶз»„жҲҗ DSP иҠҜзүҮжҲ–иҖ…еҠ йҖҹеҷЁдёӯзҡ„д»Јз ҒгҖӮ

еӣҫ 2 .жҠҠж•°жҚ®иҪ¬жҚўеҷЁж”ҫеҲ° IF зә§зҡ„жңҖеҗҺгҖӮ

еңЁе…¶жңҖеҗҺзә§пјҢжңүзӣ®зҡ„зҡ„еҜ№жҺҘ收й“ҫиҝӣиЎҢдҝ®ж”№е№¶е®һзҺ°гҖӮйҖҡиҝҮе…¶ж»ӨжіўгҖҒиҒҡжқҹе’Ңи„үеҶІеҺӢзј©зә§пјҢй“ҫзҡ„д»»еҠЎжҳҜд»ҺеҷӘеЈ°дёӯжҸҗеҸ–еҮәдҝЎеҸ·пјҢзү№еҲ«жҳҜйӮЈдәӣеҸҜиғҪжүҝиҪҪдәҶзҺҜеўғдёӯе®һйҷ…зӣ®ж ҮдҝЎжҒҜзҡ„дҝЎеҸ·гҖӮ然еҗҺпјҢйҮҚзӮ№д»ҺдҝЎеҸ·иҪ¬еҗ‘е®ғ们жүҖд»ЈиЎЁзҡ„зӣ®ж ҮпјҢд»»еҠЎзҡ„жң¬иҙЁеҸ‘з”ҹдәҶж”№еҸҳгҖӮ

д»ҺдҝЎеҸ·еҲ°зӣ®ж Ү

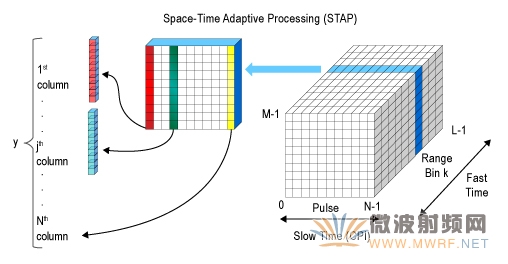

дёӢдёҖжӯҘдёҖиҲ¬жҳҜеӨҡжҷ®еӢ’еӨ„зҗҶгҖӮйҰ–е…ҲпјҢи„үеҶІиў«йҖҒе…Ҙж–№ж јйҳөеҲ—дёӯ( еӣҫ 3 ) гҖӮеңЁйҳөеҲ—дёӯпјҢжҜҸдёҖеҲ—еҗ«жңүд»ҺжҹҗдёҖеҸ‘е°„еҷЁе•Ғе•ҫиҝ”еӣһзҡ„и„үеҶІгҖӮйҳөеҲ—дёӯдјҡжңүеҫҲеӨҡеҲ—пјҢиҝҷеҸ–еҶідәҺзі»з»ҹиғҪеӨҹжүҝеҸ—еӨҡеӨ§зҡ„延时гҖӮйҳөеҲ—дёӯзҡ„иЎҢиЎЁзӨәиҝ”еӣһеҲҮжҚўж—¶й—ҙпјҡи·қзҰ»йҳөеҲ—зҡ„ x иҪҙи¶ҠиҝңпјҢеҸ‘е°„еҷЁе•Ғе•ҫе’ҢжҺҘ收и„үеҶІеҲ°иҫҫж—¶й—ҙд№Ӣй—ҙзҡ„延时е°ұи¶ҠеӨ§гҖӮиҝҷж ·пјҢе»¶ж—¶ж–№ж јд№ҹд»ЈиЎЁдәҶдёҺжҹҗдёҖи„үеҶІеҸҚе°„зҡ„зӣ®ж Үзҡ„и·қзҰ»гҖӮ

еӣҫ 3 .еӨҡжҷ®еӢ’еӨ„зҗҶж–№ж јгҖӮ

е…Ҳиҝӣзі»з»ҹеңЁйҳөеҲ—дёӯеўһеҠ дәҶеҸҰдёҖдёӘз»ҙеәҰгҖӮйҖҡиҝҮжҠҠеӨ©зәҝеҲ’еҲҶжҲҗеӯҗйҳөеҲ—пјҢзі»з»ҹеҸҜд»ҘеҗҢж—¶еҸ‘йҖҒеӨҡдёӘжіўжқҹпјҢ然еҗҺпјҢдҪҝз”ЁзӣёеҗҢзҡ„еӨҡж—Ғз“ЈеӨ©зәҝж–№еҗ‘еӣҫи®ҫзҪ®жҺҘ收еҷЁиҝӣиЎҢзӣ‘еҗ¬гҖӮжҲ–иҖ…пјҢзі»з»ҹйҖҡиҝҮиҒҡжқҹжҲ–иҖ…дҪҝз”ЁеҗҲжҲҗеӯ”еҫ„ж–№жі•жқҘжү«жҸҸжіўжқҹгҖӮзҺ°еңЁпјҢеҪ“иЈ…е…ҘеҺӢзј©еҗҺзҡ„и„үеҶІж—¶пјҢзі»з»ҹе»әз«ӢдёҖдёӘдёүз»ҙж–№ж јйҳөеҲ—пјҡдёҖдёӘиҪҙдёҠжҳҜеҸ‘йҖҒи„үеҶІпјҢ第дәҢдёӘжҳҜиҝ”еӣһ延时пјҢ第дёүдёӘжҳҜжіўжқҹж–№дҪҚ( еӣҫ 4 ) гҖӮзҺ°еңЁпјҢеҜ№дәҺжҜҸдёҖи·Ҝи„үеҶІпјҢжҲ‘们жңүдёӨз»ҙжҲ–иҖ…дёүз»ҙж–№ж јйҳөеҲ—пјҢеҗҢж—¶иЎЁзӨәи·қзҰ»е’Ңж–№еҗ‘ —— иЎЁзӨәзү©зҗҶз©әй—ҙгҖӮиҝҷз§ҚеӯҳеӮЁеҷЁзҡ„жҺ’еҲ—жҳҜз©әж—¶иҮӘйҖӮеә”еӨ„зҗҶ (STAP) зҡ„иө·зӮ№гҖӮ

еӣҫ 4 .еӨҡз»ҙж–№ж јдёәSTAPе»әз«Ӣзҹ©йҳөгҖӮ

жҰӮеҝөдёҠпјҢе®һйҷ…жғ…еҶөд№ҹжҳҜеҰӮжӯӨпјҢжһ„жҲҗиҮӘйҖӮеә”ж»ӨжіўеҷЁжҳҜдёҖдёӘзҹ©йҳөжұӮйҖҶиҝҮзЁӢпјҡиҝҷдёҖж•°жҚ®иҰҒдёҺе“ӘдёҖзҹ©йҳөзӣёд№ҳпјҢеҫ—еҲ°еҷӘеЈ°дёӯйҡҗи—Ҹзҡ„з»“жһң ? жҚ®Alteraиө„ж·ұжҠҖжңҜиҗҘй”Җз»ҸзҗҶMichael ParkerпјҢжҺЁжөӢзҡ„йҡҗи—Ҹж–№еҗ‘еӣҫдҝЎжҒҜеҸҜиғҪжқҘиҮӘеӨҡжҷ®еӢ’еӨ„зҗҶиҝҮзЁӢеҸ‘зҺ°зҡ„з§ҚеӯҗпјҢд»Һе…¶д»–дј ж„ҹеҷЁйҮҮйӣҶзҡ„ж•°жҚ®пјҢжҲ–иҖ…жқҘиҮӘжҷәиғҪж•°жҚ®гҖӮиҝҗиЎҢеңЁ CPU дёӢжёёзҡ„з®—жі•жҠҠеҒҮи®ҫзҡ„ж–№еҗ‘еӣҫжҸ’е…ҘеҲ°зҹ©йҳөж–№зЁӢдёӯпјҢи§ЈеҮәиғҪеӨҹдә§з”ҹйў„жңҹж•°жҚ®зҡ„ж»ӨжіўеҮҪж•°гҖӮ

дёӨз§ҚдҪ“зі»з»“жһ„

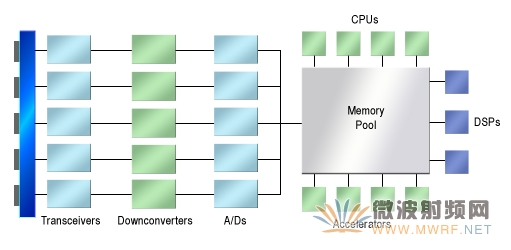

дҪңдёәеҜ№жҜ”пјҢжұҪиҪҰжҲ–иҖ…жңәеҷЁдәәзі»з»ҹи®ҫи®Ўдәәе‘ҳдјҡд»Һе®Ңе…ЁдёҚеҗҢзҡ„и§’еәҰзңӢзі»з»ҹгҖӮд»ҺеөҢе…ҘејҸи®ҫи®Ўдәәе‘ҳзҡ„и§’еәҰзңӢпјҢзі»з»ҹеҸӘжҳҜдёҖеӨ§ж®өиҪҜ件пјҢжңүдёҖдәӣйқһеёёдё“з”Ёзҡ„ I/O еҷЁд»¶пјҢд»ҘеҸҠйңҖиҰҒиҝӣиЎҢеҠ йҖҹзҡ„жҹҗдәӣд»»еҠЎгҖӮжңүз»ҸйӘҢзҡ„йӣ·иҫҫдҝЎеҸ·е·ҘзЁӢеёҲиҖғиҷ‘еҲ°дҝЎеҸ·еӨ„зҗҶе’ҢйҖҡ用硬件зҡ„зӣёеҜ№и§„жЁЎпјҢеҸҜиғҪдјҡеҜ№иҝҷдёҖж–№жі•дёҚеұ‘дёҖйЎҫгҖӮеҫҲжҳҫ然пјҢжңәиҪҪеӨҡеҠҹиғҪйӣ·иҫҫзҡ„ж•°жҚ®йҖҹзҺҮгҖҒзҒөжҙ»жҖ§е’ҢеҠЁжҖҒиҢғеӣҙиҰҒжұӮйҮҮз”Ёдё“з”Ё DSP жөҒж°ҙзәҝд»ҘеҸҠеӨ§йҮҸзҡ„жң¬ең°зј“еҶІжүҚиғҪе®ҢжҲҗе®һж—¶еӨ„зҗҶгҖӮдҪҶжҳҜеҜ№дәҺжңүеҮ дёӘеӨ©зәҝеҚ•е…ғзҡ„дёҚеҗҢеә”з”ЁпјҢз®ҖеҚ•зҡ„зҺҜеўғгҖҒжӣҙзҹӯзҡ„и·қзҰ»е’ҢиҫғдҪҺзҡ„еҲҶиҫЁзҺҮпјҢд»Ҙ CPU дёәдёӯеҝғзҡ„и§ӮзӮ№еёҰжқҘдәҶдёҖдәӣжңүж„ҸжҖқзҡ„й—®йўҳгҖӮ

е®һйҷ…з»“жһңеҸҜиғҪдёҺд»Ҙ DSP дёәдёӯеҝғзҡ„ж–№жі•е®Ңе…ЁдёҚеҗҢгҖӮдҫӢеҰӮпјҢд»Ҙ CPU дёәдёӯеҝғзҡ„ж–№жі•дёҖејҖе§ӢеҒҮи®ҫеңЁдёҖзүҮйҖҡз”Ё CPU дёҠжү§иЎҢжүҖжңүе·ҘдҪңгҖӮеҰӮжһңйҖҹеәҰдёҚеӨҹеҝ«пјҢиҝҷдёҖж–№жі•иҪ¬еҗ‘еӨҡзүҮ CPU пјҢе…ұдә«дёҖдёӘеҲҶеұӮзҡ„иҝһз»ӯеӯҳеӮЁеҷЁгҖӮеҸӘжңүеҪ“еӨҡж ёдёҚи¶ід»Ҙе®ҢжҲҗд»»еҠЎж—¶пјҢиҝҷдёҖж–№жі•жүҚиҪ¬еҗ‘дјҳеҢ–зҡ„硬件еҠ йҖҹеҷЁгҖӮ

еңЁиҰҒжұӮжңҖдёҘж јзҡ„еә”з”ЁдёӯпјҢеҗҢдёҖдёӘзі»з»ҹи®ҫи®ЎеҸҜиғҪдјҡеҗҢж—¶йҮҮз”ЁдёӨз§ҚдҪ“зі»з»“жһ„ж–№жі•гҖӮеҮ д№ҺжҜҸдёҖд»»еҠЎдёҘж јзҡ„еёҰе®Ҫе’Ңи®Ўз®—йңҖжұӮйғҪеҜјиҮҙйҮҮ用专用硬件жөҒж°ҙзәҝе’ҢеӯҳеӮЁеҷЁдҫӢеҢ–гҖӮиҰҒжұӮеӨ§е№…еәҰйҷҚдҪҺеҠҹиҖ—еҸҜиғҪдјҡиҝ«дҪҝеҒҡеҮәйҮҮз”Ёй«ҳзІҫеәҰж•°еӯ—ж–№жі•зҡ„еҶіе®ҡпјҢиҝҷдҪҝеҫ—еңЁд»»еҠЎд№Ӣй—ҙе…ұдә«зЎ¬д»¶еҸҳеҫ—и¶ҠжқҘи¶ҠеӨҚжқӮгҖӮ

Frantz жҢҮеҮәдәҶе…ідәҺжЁЎжӢҹ / ж•°еӯ—иҫ№з•Ңзҡ„й—®йўҳгҖӮд»–иҜҙпјҡ“жҲ‘们йңҖиҰҒйҮҚж–°иҖғиҷ‘жЁЎжӢҹдҝЎеҸ·еӨ„зҗҶгҖӮдёүеҚҒе№ҙд»ҘеүҚпјҢжҲ‘们ејҖе§Ӣе‘ҠиҜүзі»з»ҹи®ҫи®Ўдәәе‘ҳеҸӘиҰҒеҒҡеҘҪж•°жҚ®иҪ¬жҚўе°ұиЎҢпјҢжҲ‘们йҮҮз”Ёж•°еӯ—ж–№жі•е®ҢжҲҗе…¶д»–жүҖжңүе·ҘдҪңгҖӮдҪҶжҳҜе®һйҷ…дёҠпјҢеңЁ 8 дҪҚеҲҶиҫЁзҺҮпјҢжЁЎжӢҹе’Ңж•°еӯ—ж–№жі•еӨ§жҰӮжҳҜзӣёеҗҢзҡ„гҖӮжЁЎжӢҹжҳҜдёҚжҳҜжӣҙеҘҪдёҖдәӣ ? иҝҷеҸ–еҶідәҺеңЁжӮЁзҡ„зі»з»ҹдёӯпјҢ‘жӣҙеҘҪ'зҡ„еҗ«д№үжҳҜд»Җд№ҲгҖӮ”

еӣҫ 5 .дёҖдёӘзҗҶжғізҡ„дҪҺжҖ§иғҪAESAзі»з»ҹгҖӮ

AESA йӣ·иҫҫзі»з»ҹдёҚдҪҶдёәз ”з©¶е®һзҺ°зӯ–з•ҘжҸҗдҫӣдәҶдё°еҜҢзҡ„зҺҜеўғпјҢиҖҢдё”иҝҳжҸҗдҫӣдәҶж–№жі•жқҘз ”з©¶жңүеӨ§йҮҸдҝЎеҸ·зҡ„зі»з»ҹгҖӮиҝҷдәӣжңүжәҗйҳөеҲ—еҲҶеёғеңЁеҶӣдәӢзӯүеӨҡз§Қи®ҫи®Ўеә”з”ЁдёӯпјҢжүҖд»ҘпјҢдёҚеә”иҜҘеұҖйҷҗеңЁдј з»ҹзҡ„еөҢе…ҘејҸи®ҫи®ЎжҖқи·ҜдёӯгҖӮеӣ жӯӨпјҢеҜ№дәҺе®Ңе…ЁдёҚеҗҢзҡ„йңҖиҰҒеӨ§йҮҸдҝЎеҸ·зҡ„йўҶеҹҹиҰҒжңүж–°жҖқи·ҜпјҢиҝҷеҢ…жӢ¬дҝЎеҸ·жҷәиғҪе’ҢзҪ‘з»ңе®үе…Ёзӯүеә”з”ЁгҖӮиҝҷжҳҜеҖјеҫ—жіЁж„Ҹзҡ„йўҶеҹҹгҖӮ

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·