本章及随后几章将讨论静电放电引起的系统问题的硬件解决措施。为了便于对系统硬件解决进行讨论,将系统上的静电放电效应划分成以下三个部分:

1. 静电放电之前静电场的效应

2. 放电产生的电荷注入效应

3. 静电放电电流产生的场效应

尽管印刷线路板(PWB,通常也称之为PCB)的设计会对上述三种效应都产生影响,但是主要是对第三种效应产生影响。下面的讨论将针对第三条所述的问题给出设计指南。通常,源与接收电路之间的场耦合可以通过下列方式之一减小(这些通用方法也会在其它讨论场的章节中提到):

1. 在源端使用滤波器以衰减信号

2. 在接收端使用滤波器以衰减信号

3. 增加距离以减小耦合

4. 降低源和/或接收电路的天线效果以减小耦合

5. 将接收天线与发射天线垂直放置以减小耦合

6. 在接收天线与发射天线之间加屏蔽

7. 减小发射及接收天线的阻抗来减小电场耦合

8. 增加发射或接收天线之一的阻抗来减小磁场耦合

9. 采用一致的、低阻抗参考平面(如同多层PCB 板所提供的)耦合信号,使它们保持共模方式

在具体设计中,如电场或磁场占主导地位,应用方法7 和8 就可以解决。然而,静电放电一般同时产生电场和磁场,这说明方法7 将改善电场的抗扰度,但同时会使磁场的抗扰度降低。方法8 则与方法7 带来的效果相反。所以,方法7 和8并不是完善的解决方案。不管是电场还是磁场,使用方法1 ~ 6 与9 都会取得一定的效果,但PCB 设计的解决方法主要取决于方法3 ~ 6 和9 的综合使用。

下面详细阐述通过方法 3 ~ 6 和9 解决问题的六条实践法则及其原因所在。

一、保持环路面积最小

任意一个电路回路中有变化的磁通量穿过时,将会在环路内感应出电流。电流的大小与磁通量成正比。较小的环路中通过的磁通量也较少,因此感应出的电流也较小,这就说明环路面积必须最小。应用这一经验的困难之处是如何找到环路。

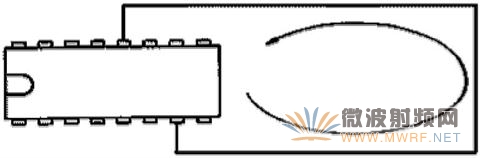

每个人都知道图16 中所示的环路,但要正确识别图17 中所示的环路则比较困难。

图 16 简单的PCB 回路

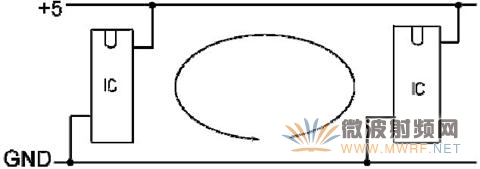

图 17 电源线与地线构成的PCB 回路

与其试着去找出所有可能的环路,还不如采取下列步骤来减小环路面积:

A、电源线与地线应紧靠在一起以减小电源和地间的环路面积。

图 18 示例说明了电源线与地线同集成电路连接的几种不同方法。

图 18 电源与地形成的环路面积的减小

粤公网安备 44030902003195号

粤公网安备 44030902003195号