0 引言

在雷达射频接收系统中,对系统性能指标的要求越来越高,其中低噪声放大器是影响着整个接收系统的噪声指标的重要因素。与普通的放大器相比,低噪声放大器作用比较突出,一方面可以减少系统的杂波干扰,提高系统的灵敏度;另一方面可以放大系统的射频信号,保证系统正常工作。因此,低噪声放大器的性能制约着整个接收系统的性能,对整个接收系统性能的提高起了决定性的作用。因此,研制宽频带、高性能、更低噪声的放大器,已经成为微波技术中发展的核心之一。

本文介绍的新型宽带低噪声放大器就是在当前工程技术发展需求的前提下,从放大器本身的特性出发,采用薄膜混合集成电路和先进的共晶微组装工艺,应用平衡式放大电路,精心研制而成的。

1 电路设计

1.1 电路原理

设计要求整个低噪声放大器的噪声系数小于2 dB,增益在32 dB以上,根据单片放大器目前的增益,需要设计三级放大链路,设计框图如图1所示。

要达到这种要求,输入匹配网络设计时必须按最小噪声系数匹配。实际上要得到最小噪声,输入网络往往都是失配的。但是由于指标要求驻波比要小于2,因此,输入网络首先要兼顾端口驻波比。对于级间匹配一,既要保证噪声要低,后级对前级的噪声贡献要低,又要保证较高的增益,其次还要兼顾两级放大器管芯间驻波比情况。对于级间匹配二,则要求保持较高的增益以及合理的增益平坦度。对于输出匹配网络,除了要保证输出功率外,还要保证整个带内的增益平坦度,以及良好的输出驻波比。

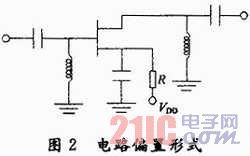

1.2 偏置电路形式

本文采用共源极接法,自偏置电路形式,单电源供电,其结构如图2所示。此处偏置网络是一个电阻电源。其优点是能够提供自动瞬时保护功能,而且,单电源供电方便。但是,电阻电源同时也会使噪声性能恶化,而且电源的旁路电容会产生低频振荡,因此,在匹配直流电路时,需要优化设计采用合适的偏置电阻,使噪声性能恶化最小。

1.3 平衡电桥设计

1.3.1 耦合器设计原理

由于采用了平衡式电路,所以,首先需要设计3 dB定向耦合器。在此选用交指线耦合器。交指线耦合器是一种多导体耦合器,其优点是:体积小;与双耦合线器件比较,它的线间距离较大,容易实现;与分支线耦合比较,它带宽宽。关于这种3 dB交指线耦合器在目前尚没有精确的设计方法。一般情况下,其耦合度按以下的三个设计方程来计算,电路的作用就是完成这种阻抗转换的。

根据以上的方程,只要知道了Zoo和Zoe,查表便可以求出物理尺寸之比,再经过仿真进行优化设计。

1.3.2 平衡电桥仿真

采用精细陶瓷基片,其介电常数为εr=9.8。利用ADS软件进行仿真如图3所示,仿真结果如图4所示。

1.4 系统仿真设计

1.4.1 稳定性设计和宽带设计

由于采用平衡电路,因此,输入、输出驻波比可以放在最后整体仿真时考虑。仿真时,重点考虑稳定性、噪声系数、增益和增益平坦度。

首先,进行稳定性设计。根据绝对稳定的充分必要条件:K>1和|△|<1。

根据其S参数(见表1),计算可得,在4~8 GHz的带宽内,0<K<1,|△|<1,潜在不稳定。在电路中加入平衡电桥做仿真显示,电路中的K>1,此时,整个电路将变成绝对稳定。因此,采用电桥将使得整个电路的稳定性设计变得简单。

再次,需要对放大器进行宽带内的设计。从本质上讲,宽带低噪声放大器的设计就是要求在一个相对较宽的频率范围内,保持放大器的增益不变。为此,应适当地设计匹配网络或者反馈网络,在保持最佳噪声系数的情况下补偿|S21|随频率的变化。一般来讲,设计宽带低噪声放大器有两种通用技术:补偿匹配网络及运用负反馈电路。在平衡电路中,噪声通常是按最佳噪声来设计的。但是,由于按最佳噪声设计往往以牺牲增益为前提,而如果按最大增益设计,往往噪声性能又将恶化。所以,为了二者兼顾,折衷考虑。按最佳噪声设计出的放大器带宽往往是很窄的,所以在做宽带匹配电路时,输入、输出端往往是失配的。本文的设计思路是:采用补偿匹配网络与负反馈电路相结合的技术,利用平衡电桥来获得最佳输入和输出VSWR;利用负反馈来补偿随频率变化的|S21|,提高系统的稳定性。二者结合最终达到所需要的设计目标。

最后,将对上述的低噪声晶体管,利用ADS进行仿真设计成一个单片,并保证良好的输入/输出比、低的噪声系数、高的增益,并把设计好的单片作为放大器的第一级。在这个前提下,再进行级联,而且,级联的第二级也需要保证设计的噪声系数小。由于总增益在32 dB以上,根据晶体管的S参数,两级增益达不到要求,因此,需要三级级联。最后一级,要有高的增益特性和良好的线性度。这样,放大器的增益特性、噪声特性、输入/输出特性,功率特性等都可以保证实现。

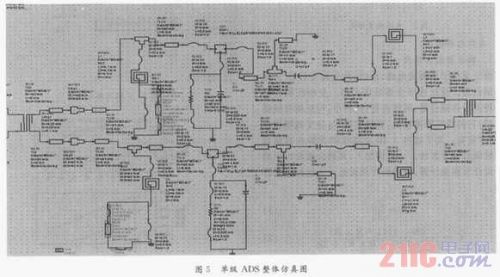

1.4.2 整体仿真

采用精细陶瓷基片,介电常数εr=9.8。选取富士通FHX系列,利用ADS进行仿真,电路原理图如图5所示。

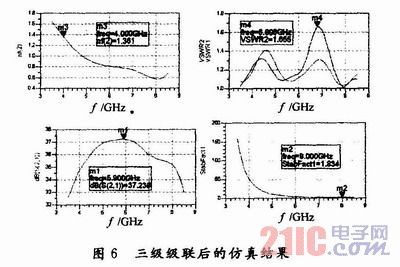

三级级联后,仿真结果如图6所示。

根据指标要求,整个电路的噪声小于1.6 dB,输入输出驻波比小于1.7,增益在35~37.1 dB之间。设计满足指标要求。

2 装配和测试结果

2.1 装配和调试

各单片加工完成之后,采用共晶工艺进行焊接,并利用导电胶将芯片粘接在底部基片上。共晶工艺具有机械强度高、热阻小、稳定性好、可靠性高等一系列的优点,是目前国际上比较先进的工艺。导电胶粘接技术工艺性好、固化容易、固化物致密、粘接力强。由于其耐热

性有限,因此导电胶的固化温度和固化时间的长短对粘接强度影响较大。一般采用合适的温度和时间来固化达到较理想的效果。

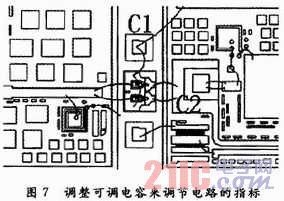

设计完成后,对带内平坦度进行调试。通过在电路中敏感部位改变容性和感性的大小来调节平坦度,使其满足指标,如图7所示。

2.2 测试结果

噪声系数测试结果见表2。

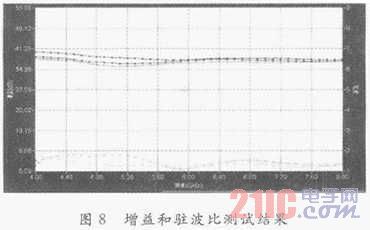

增益和驻波比测试结果如图8所示。

1dB压缩点测试,结果见表3。

测试结果表明,实验值与理论设计值吻合得较好,表明这种设计方法可取。

3 结论

C波段宽带低噪声放大器设计在国内外已有一些研究,但是该满足宽带高性能指标要求的工程设计案例还不多。该设计的宽带低噪声放大器的噪声系数、增益、增益平坦度、输入输出驻波比以及1 dB压缩点的功率均达到和超过指标要求,并且该放大器在整个C波段表现性能优良。因此,在雷达和电子对抗等工程领域可以得到广泛应用。另外,在C波段宽带低噪声放大器的小型化和集成化设计上还需进一步探索。

粤公网安备 44030902003195号

粤公网安备 44030902003195号