摘要:针对5G 毫米波通信系统对本振源频率、相位噪声、杂散抑制要求的提升,提出了一种结合ADF4002 和2 个ADF5355 频率合成器芯片,可同时用于中频和射频电路的高性能本振源。该本振源为系统中频模块提供5.4 GHz 的单音本振信号并且利用数控衰减器和放大器实现了输出功率可调,同时也利用ADF5355 的锁相环(PLL)和倍频器为射频模块提供8.4~11.2 GHz 宽频带宽、步进为100 MHz 的可调频本振信号,最终通过硬件电路的设计与调试,以及单片机(SCM)控制程序的编写,实现了低相噪、低杂散的稳定频率源。

关键词:大规模多输入多输出(MIMO);本振;锁相环;低相位噪声;频率可调

在5G 毫米波通信系统中,大规模多输入多输出(MIMO)技术被用来大幅度提高数据传输速率和信道容量。大规模MIMO 技术也是5G区别于现有系统的核心技术之一[1]。在大规模MIMO 场景下,通过基站配置数百根天线,可以使大量的终端用户使用同一个时频资源,因此系统中同时存在多路射频收发信道,也就需要多路本振信号。本振的研究是毫米波通信系统研究的关键之一[2]。

本振模块与收发系统相互独立可以有效地抑制本振泄露和射频串扰等问题,减少收发系统印制电路板(PCB)版的面积,并且可以使每个模块更灵活,便于调试和后期维护。综合考虑系统性能和成本等方面的因素,采用外置本振是现代移动通信系统中常见的选择[2-3]。

1、本振系统设计

频率合成技术主要分为直接合成技术与间接合成技术。直接合成技术又包括直接模拟合成技术与直接数字合成技术(DDS)。直接模拟合成技术是最早期的频率合成技术,其通过一系列的模拟器件进行倍频、混频、分频等算术运算从而合成固定频率,再利用窄带滤波器滤出所需频率。在这种方式下参考信号的相位噪声直接决定了输出信号的相噪,因此容易获得相噪很低的输出信号,但是这种电路的实现需要大量的模拟器件组合,集成度低,体积大,杂散抑制较差,成本高昂,目前该种技术主要用于射频微波测试测量仪器中。

直接数字合成技术的特点是通过数字方式累加相位,再利用相位和去查询正弦函数表从而得到正弦波的离散数字系列,最终经过数模(D/A)转换得到模拟正弦波。DDS 具有频点转换速率快、频率分辨率高的优点,不过由于输出频率杂散很多,输出频率较低,使其使用范围受限[4]。

间接频率合成技术即为锁相环式频率合成技术(PLL),它主要是通过相位负反馈的方式来实现对两路信号相位的跟踪,从而用锁相环将压控振荡器(VCO)的频率锁定在所需要的频点上。该种形式结构简单,相位噪声低,杂散抑制较好,成本较低,但是频率转换的时间长,频率分辨率比较低[5-6]。

结合本设计中需要输出两路频率较高的本振信号,并且其中一路带宽较宽的特点,综合相位噪声、杂散抑制等因素,决定采用锁相环频率合成技术来实现该本振源。

1.1 整体框架

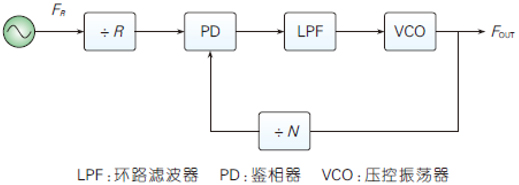

图1 是PLL 的基本结构,锁相环电路的组成部分主要包括压控振荡器(VCO)、鉴相器(PD)、环路滤波器(LPF)和分频器[5]。

图1、PLL 结构框图

参考源给出的输入信号FR 通过R 分频器降低为鉴相器的检测频率FPD ,而VCO 的输出频率经过N 分频器后得到输入鉴相器的另一路信号FN ,两路信号通过鉴相器进行相位比较,它们产生的相位差转换为电压或电流,经过低通的环路滤波器(LPF)滤除噪声和高频分量后送入VCO 用来控制VCO 的输出频率。当锁相环稳定后,即FPD 和FN 同频同相的状态下,锁相环的输出频率为:

(1)

(1)

相位噪声是衡量本振源的重要指标,收发信机的调制与解调精度(EVM)受系统的相位噪声影响,若相位噪声过大,则系统解调出的星座图会出现旋转,因此首先要降低本振源的相位噪声。影响相位噪声的因素有很多,在近端,相位噪声主要取决于参考信号、N 分频器、鉴相器以及电源。通过式(2)可以估算出环路带宽内的相位噪声:

PN = PNfloor + 10log(N) + 10log( fvco )(2)

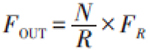

在输出频率不变的情况下,降低分频比N 可以改善相位噪声。一般来说,本振系统的参考源是全球定位系统(GPS)下行的10 MHz[5]。由于在此设计中需要较高的输出频率,为了获得良好的相位噪声,故选择提升参考频率。在整个系统前端先设计一个锁相环电路,将10 MHz 参考信号提高至100 MHz。由式(2)可知:系统的相位噪声将会降低10 dB;而在环路带宽外,相位噪声主要受VCO 影响。为了得到更好的频率稳定度和相位噪声,本设计中用100 MHz 的恒温晶体振荡器(OCXO)代替VCO[6]。

由于两路本振信号在系统中被同时使用,为了保证信号的一致性,需要采用同一个参考源,图2 为本振源结构框图。ADI 公司的频率合成器ADF4002,结合外部恒温晶振XO5051 以及GPS 参考源10 MHz,并且组成PLL 频率合成器。该模块输出100 MHz 的信号经过集总元件组成的功分器后分成2 路,分别作为2个ADF5355 的参考频率,ADF5355 是集成VCO 的宽带频率合成器。第1路参考信号通过ADF5355 的锁相环和倍频器后输出8.4~11.2 GHz 的信号,以100 MHz 步进可调的本振信号,然后经过滤波器和放大器HMC441 得到最终所需的射频本振;第2 路100 MHz 参考信号通过另一个ADF5355 的锁相环电路并且再输出5.4 GHz 的信号,再经数字衰减器HMC425A 和放大器GVA_83+,得到所需功率的中频本振。

图2、本振源结构框图

1.2 环路滤波器设计

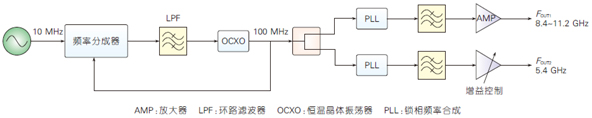

环路滤波器是锁相环电路中的重要组成单元,它可以为VCO 提供干净稳定的调谐信号,维持环路稳定性,控制环路带内外噪声,抑制参考边带杂散干扰。环路滤波器的重要参数为环路带宽和相位裕度。环路带宽的减小可以改善杂散的抑制以及VCO 近端的相位噪声,但同时增加锁定时间,并导致远端相位噪声的恶化;而环路带宽增大则会减少锁定时间,不过无法保证VCO 近端的杂散和相位噪声抑制。此外,当环路带宽为鉴相频率的1/10 到1/5 时,锁相环会失锁[4-5]。

综合环路稳定性、杂散抑制、相位噪声、锁定时间等因素,最终确定输出频率为100 MHz 的锁相环环路带宽为30 Hz,同时输出5.4 GHz 以及8.4~11.2 GHz 的PLL 环路带宽则为100 kHz。图3 给出了两路锁相环电路中四阶滤波器的结构和取值。

图3、环路滤波器结构

1.3 单片机部分设计

本设计中采用单片机C8051F320对ADF4002、2 个ADF5355 芯片以及数控衰减器HMC425A 进行输出频率和功率的控制,其中两路ADF5355 共用数据传输和串行时钟线。图4 为单片机控制电路结构图。

图4、单片机控制电路

2、测试结果与实物图

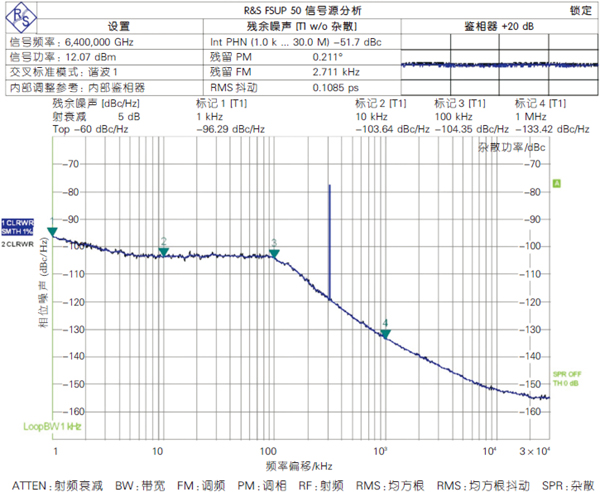

本设计实现了两路不同频率的本振信号输出,具有较好的相位噪声。利用RS 的相位噪声分析仪分别对两路输出信号的相位噪声进行了测量,结果如图5、6 所示。在8.4~11.2 GHz 频带内选择10 GHz 信号的相位噪声测试结果,参考频率源为相噪仪自带的10 MHz。

图5、ADF5355 输出5.4 GHz 相位噪声

图6、ADF5355 输出10 GHz 相位噪声

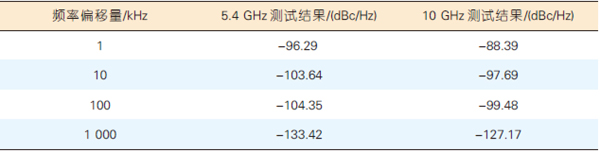

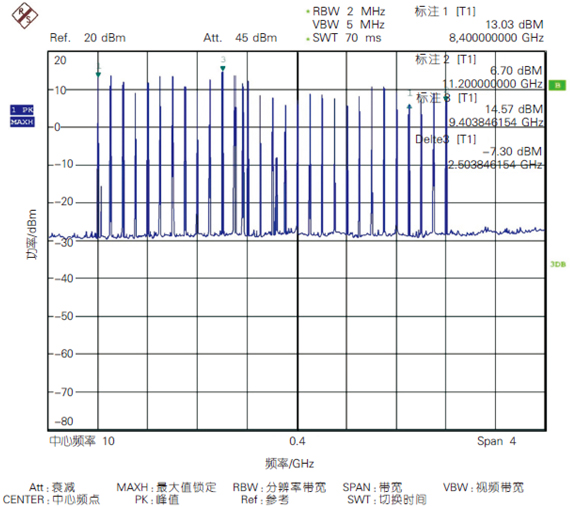

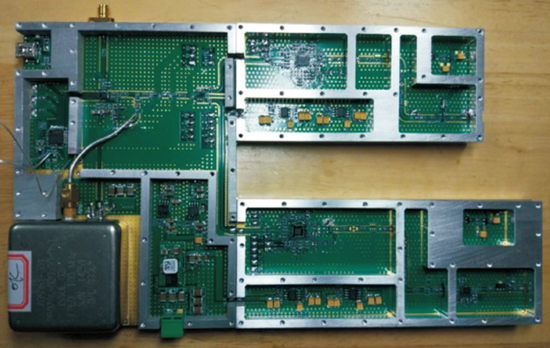

从图5、6 中可以知道:5.4 GHz 信号输出功率为12.07 dBm,10 GHz的信号输出功率约为13.8 dBm, 并且两路ADF5355 锁相环电路的输出信号皆具有良好的相位噪声,具体结果如表1所示。通过上位机进行频率控制,利用相噪仪对频率范围为8.4~11.2 GHz,步进100 MHz 的本振信号输出功率进行了测试,结果如图7 所示。在该频带内输出最大功率为14.57 dBm,最小功率为6.7 dBm。值得注意的是:在该频带内信号输出功率浮动较大,这主要是由于ADF5355 的输出功率有8 dBm 的变化范围。在后续链路设计中可以结合数控衰减器来平衡各个频点的输出功率。此外,图中谱线的不清晰主要是由于上位机变换频率的速度大于本振信号锁定的速度,在实际应用中可以等单个频点锁定后,再进行频率切换,以保证本振信号良好的性能。图8 为本振源实物图。

表1、本振源相位噪声测试结果

图7、8.4~11.2 GHz 本振信号输出功率

图8、本振系统实物图

3、结束语

文中通过结合3 个锁相环结构成功实现了参考频率的提升和2 个不同频段本振源的输出,可同时用于中频以及射频模块,并且降低了相位噪声。输出的两路本振信号中,一路5.4 GHz 信号功率可调,另一路8.4~11.2 GHz 信号可实现较宽频带内本振源的输出。在后续研究中,我们可以通过功分模块,配合放大器实现多路同频同相的本振信号的输出以满足大规模MIMO 系统对于本振的相关需求。

参考文献

[1] 尤肖虎.5G 移动通信发展趋势与若干关键技术[J].中国科学,2014,5(44):551-563[2] 刘兆栋.面向5G 移动通信系统的本振技术研究[C]//2015 年全国微波毫米波会议论文集.合肥:中国电子学会,2015

[3] 单月忠.基于ADF4351 的频率源设计与实现[J].无线电通信技术,2014,40(6):85-88

[4] 赵清潇.基于宽带多通道微波收发信机的本振源设计与实现[D].青岛:山东大学,2015

[5] 褚颖颖.大规模MIMO 系统射频关键技术研究[D].南京:东南大学,2015

[6] 林波.大规模MIMO 外部本振的研究[D].南京:东南大学, 2018

[7] 黄维辰.面向下一代移动通信系统的多通道射频收发信机以及频率源的研究[D].南京:东南大学,2017

[8] BANERJEE D. PLL Performance, Simulation, and Design 5th Edition [M]. USA: National, 2017:3-8

作者:胡蒙筠、周健义,东南大学

来源:中兴通讯技术

粤公网安备 44030902003195号

粤公网安备 44030902003195号