5GжҜ«зұіжіўж— зәҝз”өе°„йў‘жҠҖжңҜ

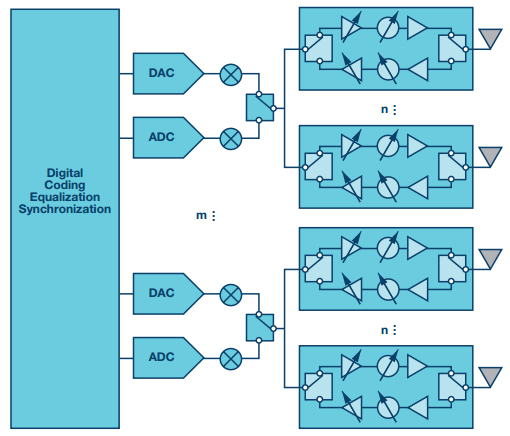

дёҡз•Ңжҷ®йҒҚи®ӨдёәпјҢж··еҗҲжіўжқҹиөӢеҪўпјҲдҫӢеҰӮеӣҫ1жүҖзӨәпјүе°ҶжҳҜе·ҘдҪңеңЁеҫ®жіўе’ҢжҜ«зұіжіўйў‘зҺҮзҡ„5Gзі»з»ҹзҡ„йҰ–йҖүжһ¶жһ„гҖӮиҝҷз§Қжһ¶жһ„з»јеҗҲиҝҗз”Ёж•°еӯ— (MIMO) е’ҢжЁЎжӢҹжіўжқҹиөӢеҪўжқҘе…ӢжңҚй«ҳи·Ҝеҫ„жҚҹиҖ—并жҸҗй«ҳйў‘и°ұж•ҲзҺҮгҖӮеҰӮеӣҫ1жүҖзӨәпјҢmдёӘж•°жҚ®жөҒзҡ„з»„еҗҲеҲҶеүІеҲ°nжқЎRFи·Ҝеҫ„дёҠд»ҘеҪўжҲҗиҮӘз”ұз©әй—ҙдёӯзҡ„жіўжқҹпјҢж•…еӨ©зәҝе…ғ件жҖ»ж•°дёәд№ҳз§Ҝm × nгҖӮж•°еӯ—жөҒеҸҜйҖҡиҝҮеӨҡз§Қж–№ејҸз»„еҗҲпјҢж—ўеҸҜеҲ©з”Ёй«ҳеұӮMIMOе°ҶжүҖжңүиғҪйҮҸеҜјеҗ‘еҚ•дёӘз”ЁжҲ·пјҢд№ҹеҸҜд»ҘеҲ©з”ЁеӨҡз”ЁжҲ·MIMOж”ҜжҢҒеӨҡдёӘз”ЁжҲ·гҖӮ

еӣҫ1. ж··еҗҲжіўжқҹиөӢеҪўжЎҶеӣҫ

жң¬ж–Үе°ҶиҖғеҜҹдёҖдёӘз®ҖеҚ•зҡ„еӨ§и§„жЁЎеӨ©зәҝйҳөеҲ—зӨәдҫӢпјҢеҖҹд»ҘжҺўи®ЁжҜ«зұіжіўж— зәҝз”өзҡ„жңҖдјҳжҠҖжңҜйҖүжӢ©гҖӮзҺ°еңЁж·ұе…ҘжҹҘзңӢжҜ«зұіжіўзі»з»ҹж— зәҝз”өйғЁеҲҶзҡ„жЎҶеӣҫпјҢжҲ‘们зңӢеҲ°дёҖдёӘз»Ҹе…ёи¶…еӨ–е·®з»“жһ„е®ҢжҲҗеҫ®жіўдҝЎеҸ·еҲ°ж•°еӯ—дҝЎеҸ·зҡ„еҸҳжҚўпјҢ 然еҗҺиҝһжҺҘеҲ°еӨҡи·Ҝе°„йў‘дҝЎеҸ·еӨ„зҗҶи·Ҝеҫ„пјҢиҝҷйҮҢдё»иҰҒжҳҜиҝҗз”Ёеҫ®жіўз§»зӣёеҷЁе’ҢиЎ°еҮҸеҷЁжқҘе®һзҺ°жіўжқҹиөӢеҪўгҖӮ дј з»ҹдёҠпјҢжҜ«зұіжіўзі»з»ҹжҳҜеҲ©з”ЁеҲҶз«ӢеҷЁд»¶жһ„е»әпјҢеҜјиҮҙе…¶е°әеҜёиҫғеӨ§дё” жҲҗжң¬иҫғй«ҳгҖӮиҝҷж ·зҡ„зі»з»ҹйҮҢйқўзҡ„еҷЁд»¶дҪҝз”ЁCMOSгҖҒSiGe BiCMOSе’Ң GaAsзӯүжҠҖжңҜпјҢдҪҝжҜҸдёӘеҷЁд»¶йғҪиғҪеҫ—еҲ°иҫғдјҳзҡ„жҖ§иғҪгҖӮдҫӢеҰӮпјҢж•°жҚ®иҪ¬жҚўеҷЁзҺ°еңЁйҮҮз”ЁCMOSе·ҘиүәејҖеҸ‘пјҢдҪҝйҮҮж ·йҖҹзҺҮиҫҫеҲ°GHzиҢғеӣҙгҖӮдёҠдёӢеҸҳйў‘е’ҢжіўжқҹиөӢеҪўеҠҹиғҪеҸҜд»ҘеңЁSiGe BiCMOSдёӯжңүж•Ҳе®һзҺ°гҖӮж №жҚ®зі»з»ҹжҢҮж ҮиҰҒжұӮпјҢеҸҜиғҪйңҖиҰҒеҹәдәҺGaAsеҠҹзҺҮж”ҫеӨ§еҷЁе’ҢдҪҺеҷӘеЈ°ж”ҫеӨ§еҷЁпјҢдҪҶеҰӮжһң SiGe BiCMOSиғҪеӨҹж»Ўи¶іиҰҒжұӮпјҢеҲ©з”Ёе®ғе°ҶиғҪе®һзҺ°иҫғй«ҳзҡ„йӣҶжҲҗеәҰгҖӮ

еҜ№дәҺ5GжҜ«зұіжіўзі»з»ҹпјҢдёҡз•ҢеёҢжңӣе°Ҷеҫ®жіўеҷЁд»¶е®үиЈ…еңЁеӨ©зәҝеҹәжқҝиғҢйқўпјҢиҝҷиҰҒжұӮеҫ®жіўиҠҜзүҮзҡ„йӣҶжҲҗеәҰеҝ…йЎ»еӨ§еӨ§жҸҗй«ҳгҖӮдҫӢеҰӮпјҢдёӯеҝғйў‘зҺҮдёә 28 GHzзҡ„еӨ©зәҝзҡ„еҚҠжіўйҳөеӯҗй—ҙи·қзәҰдёә5 mmгҖӮйў‘зҺҮи¶Ҡй«ҳпјҢжӯӨй—ҙи·қи¶Ҡе°ҸпјҢиҠҜзүҮжҲ–е°ҒиЈ…е°әеҜёеӣ иҖҢжҲҗдёәйҮҚиҰҒиҖғиҷ‘еӣ зҙ гҖӮзҗҶжғіжғ…еҶөдёӢпјҢеҚ•жіўжқҹзҡ„ж•ҙдёӘжЎҶеӣҫйғҪеә”еҪ“йӣҶжҲҗеҲ°еҚ•дёӘICдёӯпјӣе®һйҷ…жғ…еҪўдёӯпјҢиҮіе°‘еә”е°ҶдёҠдёӢеҸҳйў‘еҷЁе’ҢRFеүҚз«ҜйӣҶжҲҗеҲ°еҚ•дёӘRFICдёӯгҖӮйӣҶжҲҗеәҰе’Ңе·ҘиүәйҖүжӢ©еңЁжҹҗз§ҚзЁӢеәҰдёҠжҳҜз”ұеә”з”ЁеҶіе®ҡзҡ„пјҢеңЁдёӢйқўзҡ„зӨәдҫӢеҲҶжһҗдёӯжҲ‘们е°ҶдҪ“дјҡеҲ°иҝҷдёҖзӮ№гҖӮ

зӨәдҫӢеҲҶжһҗпјҡеӨ©зәҝдёӯеҝғйў‘зҺҮдёә28 GHzпјҢ EIRPдёә60 dBm

жӯӨеҲҶжһҗиҖғиҷ‘дёҖдёӘе…ёеһӢеҹәз«ҷеӨ©зәҝзі»з»ҹпјҢEIRPиҰҒжұӮдёә60 dBmгҖӮдҪҝз”ЁеҰӮдёӢеҒҮи®ҫжқЎд»¶пјҡ

- - еӨ©зәҝйҳөеӯҗеўһзӣҠ = 6 dBiпјҲзһ„еҮҶзәҝпјү

- - жіўеҪўPAPR = 10 dBпјҲйҮҮз”ЁQAMзҡ„OFDMпјү

- - P1dBж—¶зҡ„еҠҹзҺҮж”ҫеӨ§еҷЁPAE = 30%

- - еҸ‘е°„/жҺҘ收ејҖе…іжҚҹиҖ— = 2 dB

- - еҸ‘е°„/жҺҘ收еҚ з©әжҜ” = 70%/30%

- - ж•°жҚ®жөҒ = 8

- - еҗ„з”өи·ҜжЁЎеқ—зҡ„еҠҹиҖ—еҹәдәҺзҺ°жңүжҠҖжңҜгҖӮ

иҜҘжЁЎеһӢд»Ҙ8дёӘж•°жҚ®жөҒдёәеҹәзЎҖжқҘжһ„е»әпјҢиҝһжҺҘеҲ°дёҚеҗҢж•°йҮҸзҡ„RFй“ҫгҖӮжЁЎеһӢдёӯзҡ„еӨ©зәҝж•°йҮҸд»Ҙ8зҡ„еҖҚж•°жү©еӨ§пјҢжңҖеӨҡ512дёӘе…ғ件гҖӮ

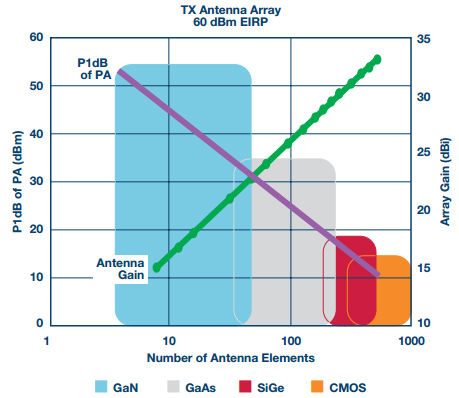

еӣҫ2жҳҫзӨәдәҶеҠҹзҺҮж”ҫеӨ§еҷЁзәҝжҖ§еәҰйҡҸзқҖеӨ©зәҝеўһзӣҠжҸҗй«ҳиҖҢеҸҳеҢ–зҡ„жғ…еҶөгҖӮ жіЁж„Ҹпјҡз”ұдәҺејҖе…іжҚҹиҖ—пјҢж”ҫеӨ§еҷЁзҡ„иҫ“еҮәеҠҹзҺҮиҰҒжҜ”жҸҗдҫӣз»ҷеӨ©зәҝзҡ„еҠҹзҺҮй«ҳ2 dBгҖӮеҪ“з»ҷеӨ©зәҝеўһеҠ е…ғ件时пјҢж–№еҗ‘жҖ§еўһзӣҠйҡҸзқҖXиҪҙеҜ№ж•°еҖјжҸҗй«ҳиҖҢзәҝжҖ§жҸҗй«ҳпјҢеӣ жӯӨпјҢеҗ„ж”ҫеӨ§еҷЁзҡ„еҠҹиҖ—иҰҒжұӮйҷҚдҪҺгҖӮ

еӣҫ2. еӨ©зәҝеўһзӣҠдёҺеҠҹзҺҮж”ҫеӨ§еҷЁиҫ“еҮәж°ҙе№іиҰҒжұӮзҡ„е…ізі»

дёәдәҶдҫҝдәҺиҜҙжҳҺпјҢжҲ‘们еңЁжӣІзәҝдёҠеҸ еҠ дәҶжҠҖжңҜеӣҫпјҢжҢҮзӨәе“Әз§ҚжҠҖжңҜеҜ№дёҚ еҗҢиҢғеӣҙзҡ„еӨ©зәҝе…ғ件数йҮҸжңҖдҪігҖӮжіЁж„ҸпјҡдёҚеҗҢжҠҖжңҜд№Ӣй—ҙеӯҳеңЁйҮҚеҸ пјҢиҝҷ жҳҜеӣ дёәжҜҸз§ҚжҠҖжңҜйғҪжңүдёҖдёӘйҖӮз”Ёзҡ„еҖјиҢғеӣҙгҖӮеҸҰеӨ–пјҢж №жҚ®е·Ҙиүәе’Ңз”өи·Ҝи®ҫи®Ўе®һи·өпјҢе…·дҪ“жҠҖжңҜеҸҜд»Ҙе®һзҺ°зҡ„жҖ§иғҪд№ҹжңүдёҖдёӘиҢғеӣҙгҖӮе…ғ件йқһеёёе°‘ж—¶пјҢеҗ„й“ҫйңҖиҰҒй«ҳеҠҹзҺҮPAпјҲGaNе’ҢGaAsпјүпјҢдҪҶеҪ“е…ғ件数йҮҸи¶…иҝҮ200ж—¶пјҢ P1dBйҷҚеҲ°20dBmд»ҘдёӢпјҢеӨ„дәҺзЎ…е·ҘиүәеҸҜд»Ҙж»Ўи¶ізҡ„иҢғеӣҙгҖӮеҪ“е…ғ件数йҮҸ и¶…иҝҮ500ж—¶пјҢPAжҖ§иғҪеӨ„дәҺеҪ“еүҚCMOSжҠҖжңҜе°ұиғҪе®һзҺ°зҡ„иҢғеӣҙгҖӮ

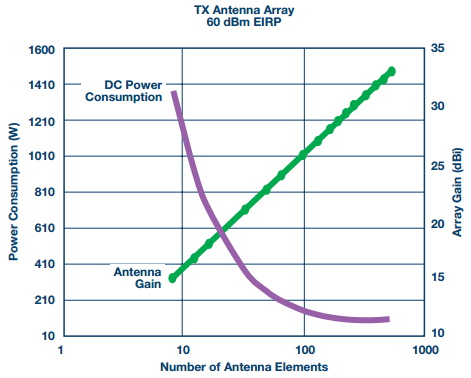

зҺ°еңЁиҖғиҷ‘е…ғ件еўһеҠ ж—¶еӨ©зәҝTxзі»з»ҹзҡ„еҠҹиҖ—пјҢеҰӮеӣҫ3жүҖзӨәгҖӮеҗҢйў„жңҹдёҖж ·пјҢеҠҹиҖ—дёҺеӨ©зәҝеўһзӣҠжҲҗеҸҚжҜ”е…ізі»пјҢдҪҶжңүдёҖдёӘйҷҗеҖјгҖӮи¶…иҝҮж•°зҷҫе…ғ件时пјҢPAзҡ„еҠҹиҖ—дёҚеҶҚеҚ дё»еҜјең°дҪҚпјҢеҜјиҮҙж•ҲзӣҠйҖ’еҮҸгҖӮ

еӣҫ3. еӨ©зәҝеўһзӣҠдёҺеӨ©зәҝTxйғЁеҲҶзӣҙжөҒеҠҹиҖ—зҡ„е…ізі»

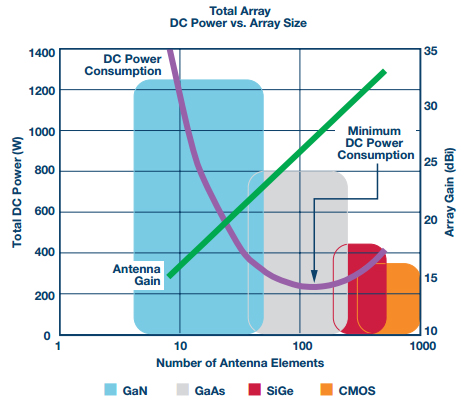

ж•ҙдёӘзі»з»ҹзҡ„еҠҹиҖ—еҰӮеӣҫ4жүҖзӨәпјҲеҢ…жӢ¬еҸ‘е°„жңәе’ҢжҺҘ收жңәпјүгҖӮеҗҢйў„жңҹдёҖж ·пјҢжҺҘ收жңәзҡ„еҠҹиҖ—йҡҸзқҖRFй“ҫзҡ„еўһеҠ иҖҢзәҝжҖ§жҸҗй«ҳгҖӮиӢҘе°ҶдёҚж–ӯдёӢйҷҚзҡ„TxеҠҹиҖ—жӣІзәҝеҸ еҠ еңЁдёҚж–ӯдёҠеҚҮзҡ„RxеҠҹиҖ—жӣІзәҝдёҠпјҢжҲ‘们дјҡи§ӮеҜҹеҲ°дёҖдёӘжңҖдҪҺеҠҹиҖ—еҢәеҹҹгҖӮ

жң¬дҫӢдёӯпјҢжңҖдҪҺеҖјеҮәзҺ°еңЁеӨ§зәҰ128дёӘе…ғ件时гҖӮеӣһйЎҫеӣҫ2з»ҷеҮәзҡ„жҠҖжңҜеӣҫпјҢиҰҒеҲ©з”Ё128дёӘе…ғ件е®һзҺ°60dBmзҡ„EIRPпјҢжңҖдҪіPAжҠҖжңҜжҳҜGaAsгҖӮ

иҷҪ然дҪҝз”ЁGaAs PAеҸҜд»Ҙе®һзҺ°жңҖдҪҺзҡ„еӨ©зәҝеҠҹиҖ—е’Ң60dBm EIRPпјҢдҪҶиҝҷеҸҜиғҪж— жі•ж»Ўи¶ізі»з»ҹи®ҫи®Ўзҡ„е…ЁйғЁиҰҒжұӮгҖӮеүҚйқўжҸҗеҲ°пјҢеҫҲеӨҡжғ…еҶөдёӢиҰҒжұӮе°ҶRFICж”ҫеңЁеӨ©зәҝе…ғ件зҡ„λ/2й—ҙи·қд»ҘеҶ…гҖӮдҪҝз”ЁGaAsеҸ‘е°„/жҺҘ收模еқ—еҸҜжҸҗдҫӣжүҖйңҖзҡ„жҖ§иғҪпјҢдҪҶдёҚж»Ўи¶іе°әеҜёзәҰжқҹжқЎд»¶гҖӮдёәдәҶеҲ©з”ЁGaAsеҸ‘е°„/жҺҘ收模еқ—пјҢйңҖиҰҒйҮҮз”Ёе…¶д»–е°ҒиЈ…е’Ңеёғзәҝж–№жЎҲгҖӮ

дјҳе…ҲйҖүжӢ©еҸҜиғҪжҳҜеўһеҠ еӨ©зәҝе…ғ件数йҮҸд»ҘдҪҝз”ЁйӣҶжҲҗеҲ°RFICдёӯзҡ„SiGe BiCMOSеҠҹзҺҮж”ҫеӨ§еҷЁгҖӮеӣҫ4жҳҫзӨәпјҢиӢҘе°Ҷе…ғ件数йҮҸеҠ еҖҚпјҢиҫҫеҲ°зәҰ256 ж—¶пјҢSiGeж”ҫеӨ§еҷЁдҫҝиғҪж»Ўи¶іиҫ“еҮәеҠҹзҺҮиҰҒжұӮгҖӮеҠҹиҖ—зҡ„еўһе№…еҫҲе°ҸпјҢиҖҢдё”еҸҜд»ҘжҠҠSiGe BiCMOS RFICж”ҫеҲ°еӨ©зәҝе…ғ件 (28 GHz) зҡ„λ/2й—ҙи·қд»ҘеҶ…гҖӮ

е°ҶиҝҷдёҖеҒҡжі•жү©еұ•еҲ°CMOSпјҢжҲ‘们еҸ‘зҺ°CMOSд№ҹиғҪе®һзҺ°ж•ҙдҪ“60dBm EIRPпјҢдҪҶд»ҺжҠҖжңҜеӣҫзңӢпјҢе…ғ件数йҮҸиҝҳиҰҒеҠ еҖҚгҖӮеӣ жӯӨпјҢиҝҷз§Қж–№жЎҲдјҡеҜјиҮҙе°әеҜёе’ҢеҠҹиҖ—еўһеҠ пјҢиҖғиҷ‘еҲ°з”өжөҒжҠҖжңҜйҷҗеҲ¶пјҢCMOSж–№жі•дёҚжҳҜеҸҜиЎҢзҡ„йҖүжӢ©гҖӮ

еӣҫ4. ж•ҙдёӘеӨ©зәҝйҳөеҲ—зҡ„зӣҙжөҒеҠҹиҖ—дёҺеӨ©зәҝеўһзӣҠзҡ„е…ізі»

жҲ‘们зҡ„еҲҶжһҗиЎЁжҳҺпјҡеҗҢж—¶иҖғиҷ‘еҠҹиҖ—е’ҢйӣҶжҲҗе°әеҜёзҡ„иҜқпјҢеҪ“еүҚе®һзҺ°60dBm EIRPеӨ©зәҝзҡ„жңҖдҪіж–№жЎҲжҳҜе°ҶSiGe BiCMOSжҠҖжңҜйӣҶжҲҗеҲ°RFICдёӯгҖӮ 然иҖҢпјҢеҰӮжһңиҖғиҷ‘е°ҶжӣҙдҪҺеҠҹиҖ—зҡ„еӨ©зәҝз”ЁдәҺCPEпјҢйӮЈд№ҲCMOSеҪ“然жҳҜеҸҜиЎҢзҡ„ж–№жЎҲгҖӮ

иҝҷдёҖеҲҶжһҗжҳҜеҹәдәҺеҪ“еүҚеҸҜз”ЁжҠҖжңҜпјҢдҪҶжҜ«зұіжіўзЎ…е·Ҙиүәе’Ңи®ҫи®ЎжҠҖжңҜжӯЈеңЁеҸ–еҫ—йҮҚеӨ§иҝӣжӯҘгҖӮжҲ‘们预计жңӘжқҘзҡ„зЎ…е·ҘиүәдјҡжңүжӣҙеҘҪзҡ„иғҪж•Ҳе’Ңжӣҙй«ҳзҡ„ иҫ“еҮәеҠҹзҺҮиғҪеҠӣпјҢе°ҶиғҪе®һзҺ°жӣҙе°Ҹзҡ„е°әеҜёе№¶иҝӣдёҖжӯҘдјҳеҢ–еӨ©зәҝе°әеҜёгҖӮ

йҡҸзқҖ5Gзҡ„еҲ°жқҘж—ҘзӣҠдёҙиҝ‘пјҢи®ҫи®Ўдәәе‘ҳе°ҶжҢҒз»ӯйҒҮеҲ°жҢ‘жҲҳгҖӮдёәжҜ«зұіжіўж— зәҝз”өеә”з”ЁзЎ®е®ҡжңҖдҪіжҠҖжңҜж–№жЎҲж—¶пјҢиҖғиҷ‘дҝЎеҸ·й“ҫзҡ„жүҖжңүж–№йқўе’ҢдёҚеҗҢICе·Ҙиүәзҡ„еҗ„з§ҚдјҳеҠҝжҳҜжңүзӣҠзҡ„гҖӮйҡҸзқҖ5Gз”ҹжҖҒзі»з»ҹдёҚж–ӯеҸ‘еұ•пјҢADIе…¬еҸёдҫқжүҳзӢ¬жңүзҡ„жҜ”зү№еҲ°жҜ«зұіжіўиғҪеҠӣпјҢиҮҙеҠӣдәҺдёәе®ўжҲ·жҸҗдҫӣе№ҝжіӣзҡ„жҠҖжңҜз»„еҗҲпјҲеҢ…жӢ¬еҗ„з§Қз”өи·Ҝи®ҫи®Ўе·Ҙиүәпјүе’Ңзі»з»ҹеҢ–ж–№жі•гҖӮ

дҪңиҖ…пјҡADIе…¬еҸёйҖҡдҝЎдәӢдёҡйғЁCTO Thomas CameronеҚҡеЈ«

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·

зІӨе…¬зҪ‘е®үеӨҮ 44030902003195еҸ·