"借助FPGA技术和LabVIEW图形化系统设计方法,ST Kinetics开发了一种LVDS数据总线,用于实现多通道宽带射频系统处理子系统之间的大型射频数据共享。"- Wai Hlaing Thet, ST Kinetics

挑战:

需要具有高带宽和可靠性的数据总线来将原始RF数据或经处理的RF数据从一个处理子系统钟的FPGA传输到另一个子系统的FPGA上。

解决方案:

使用FlexRIO FPGA模块和LVDS数字接口模块部署解决方案。ST Kinetic设计和实现了LVDS数据总线来将射频数据实时、连续地从一个处理子系统传输到另一个子系统进行实时监测、分析和信号处理。

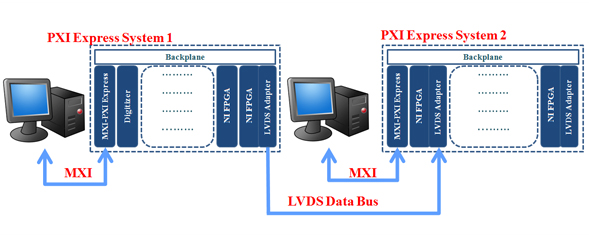

现今,使用FPGA技术进行射频数据信号处理已经非常普遍,因为该技术可实现高速计算能力。通常情况下,处理大量RF数据需要部署的FGPA资源越来越多。因此,FPGA模块会跨多个处理子系统进行部署。借助FlexRIO FPGA模块和LVDS数字接口模块,ST Kinetics成功地设计并实现了一个解决方案,以促进多通道宽带RF系统的处理子系统之间的实时数据传输。图1显示的系统结构用于开发LVDS数据总线,继而实现处理子系统之间的大型RF数据共享。

图1. 基于多通道宽带RF系统架构的LVDS数据总线实现

LVDS数据总线与10 G网络和共享内存的比较

10 G网络或共享内存也可以用于实现处理子系统之间的大量射频数据传输。但是,10 G网络和共享内存需要在将数据传输至其他处理子系统之前将数据路由到主计算机。因此,通过10 G网或共享内存连续传输大量RF数据需要非常大的计算资源开销(CPU处理能力和内存)。

基于专用LVDS数据总线的数据共享可避免这个麻烦。因此,CPU和内存资源可以用来执行其他计算任务。换而言之,基于LVDS数据总线的RF数据共享在在资源使用方面更加高效。

LVDS数据总线是高速数据通信的通用接口标准。实现高射频信号处理可靠性需要LVDS数据总线具有数据完整性。ST Kinetics成功开发了所需的智能算法,保证了LVDS数据总线上的数据完整性。

实现

在本案例分析中,该解决方案部署到基于PXI Express系统的双机箱配置中。每个PXI Express系统形成一个单独的处理系统,其中部署了一组FlexRIO设备以及相应的LVDS FPGA接口模块。两个处理子系统通过两条LVDS电缆互连。

ST Kinetics智能算法部署到FlexRIO FPGA模块上进行RF数据采集。除了LVDS接口模块和FPGA上的专用数据传输算法,FlexRIO模块还提供了LVDS数据总线。

RF数据可以通过这一条LVDS数据总线实时传输到另一个处理子系统。由于不需要将数据路由到主计算机上,专用LVDS数据总线非常适用于多机箱配置。

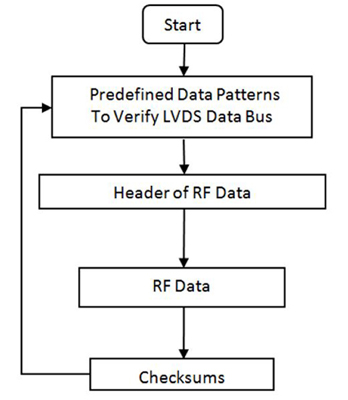

图2显示的是部署到FGPA上的一种特殊数据传输算法,用于确保有效的高速数据传输,同时保持数据的完整性。

图2. 基于LVDS数据总线的数据传输序列,具有数据完整性检查功能

RF数据可经由LVDS数据总线连续、实时地传输。在每个时间间隔内,LVDS数据总线经验证可使用预先定义的数据模式确保数据完整性。这些预定义的数据模式可用作为LVDS数据总线的自诊断。接着传输的是RF数据标题和RF数据内容。然后,系统使用奇偶校验位校验和算法来保证数据的完整性。在每个时间间隔内,根据所传送的射频数据产生的校验值会进行反复核对,以验证数据的完整性。因而,数据传输过程中出现的数据损坏可立即检测到。

结论

借助FPGA技术和LabVIEW图形化系统设计方法,ST Kinetics开发了一种LVDS数据总线,用于实现多通道宽带射频系统处理子系统之间的大型射频数据共享,从而将RF数据传输到所有处理子系统中进行实时监测、分析和处理。

系统架构具有高度可扩展性,以满足需要更高数据传输速率的其他处理子系统的需求。

作者:Thet Wa. Hlaing - ST Kinetics

粤公网安备 44030902003195号

粤公网安备 44030902003195号