引言

设想一下,某个设备可以使您在家里实现高质量的手机接听,并允许您和您的家人无限制地使用语音和数据通信,而且月费用很低。毫微微基站就是这样的设备,甚至还能提供更多的功能,它通常也称为毫微微蜂窝基站。当将这种小型的无线设备放置于家庭或办公室内时,它能改善本地无线覆盖率,这有望显著改变无线基础设施的产业格局。

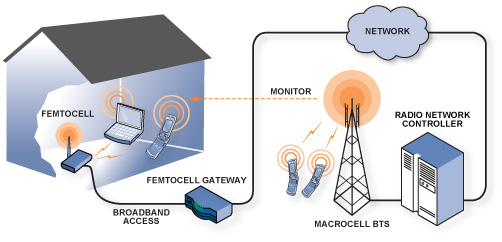

图1展示了毫微微蜂窝的概念。传统的基站提供更大范围的覆盖,而毫微微蜂窝可在更小的区域内提供无线覆盖,例如住宅。毫微微蜂窝通过用户的宽带互联网连接将手机信息流传递到网络,因而减轻无线网络的负载。毫微微蜂窝改善了网络的容量,同时减少了信号的回程路径,降低了功耗以及运营商的维护成本。它还使运营商可以参与家庭通信业务的竞争,在这个领域他们的信号覆盖通常有限。运营商可以通过增加用户的手机月费来补贴毫微微蜂窝的投入成本。当处于毫微微蜂窝区域时,所有的手机费用都被包括在家庭开销预算内,允许无限制地使用语音和数据,而不会产生很高的月费用。由于距离毫微微蜂窝很近,因此可以达到很高的连接质量,这同时可以降低手机的电池耗电量。毫微微蜂窝还克服了3G信号从基站穿透墙体的制约,因而可以实现非常高速的无线数据业务,例如浏览互联网、下载音乐以及手机接收视频流等。

图1:毫微微蜂窝基站与宏蜂窝基站的对比。

毫微微蜂窝与Wi-Fi路由器类似,是基于经过验证的无线基础架构标准,例如UMTS、CDMA。而且它与新出现的标准兼容,利用运营商拥有的频段提供有效的、鲁棒性的无线连接。由于与现存的手机是兼容的,因此这种连接对于用户来说是透明的。不像宏蜂窝通常将数十或者数百个基站汇集到一张核心网中,毫微微蜂窝网关必须管理数千甚至数百万个的毫微微蜂窝节点。

毫微微蜂窝必须提供与手机基站相近的服务质量(QoS),并且成本也相近,这对于无线设计工程师来说是一个独特挑战。毫微微蜂窝必须提供高质量的语音服务和高速移动数据服务(EVOD和HSPA),而成本仅为宏节点的几分之一。为了解决这些挑战,毫微微蜂窝的设计必须利用低成本的制造技术和高度集成的电路来降低调校和测试时间。由于毫微微蜂窝设备应用于家庭,因此必须体积小巧、成本低廉,以及用户可自行安装。毫微微蜂窝的发射功率很低,在100mW级别,因此其设计必须注意到无线环境问题,以便降低无线干扰,满足无线管制要求。3G毫微微蜂窝还必须能监控UMTS信道以检测附近的基站,以及检测GSM信道,这样当用户离开毫微微蜂窝区域时,可以进行恰当的网络切换。

毫微微蜂窝可以被视为由两个截然不同的功能组成:模拟前端和基带处理器。前端部分,即本文讨论的主题,将数字数据流转换成发射电路中的RF信号,在接收链路中则相反。前端设计需要在集成度和性能之间进行折衷。尽管分立解决方案可以根据需要进行调整来提供最佳的性能,但是其成本对于毫微微蜂窝来说是不可接受的。相反,一个完全集成的解决方案可以带来最低的成本,但是性能可能达不到要求。

图2:基于ADI芯片组的毫微微蜂窝模拟前端的功能框图。

图2所示的是一个毫微微蜂窝设备的一个高层次功能框图,设计用于支持工作于UMTS频段的本地基站,以及监测在850MHz、900MHz、1800MHz、1900MHz和2100MHz频段的信号。混合信号前端(MxFE®)基带收发器 AD98631与 ADF4602-12集成无线收发器、ADL55423和ADL53204线性放大器、开关、滤波器和其它相关的支持电路共同组成了用于毫微微蜂窝的紧凑而高性能的前端。接下来将对图中高亮的模块进行详细描述。

在发射端,数字基带将12位的并行数据流发送到AD9863中,AD9863再将这些数据流转换成模拟I/Q基带信号。基带信号由ADF4602-1转换为RF信号,并由ADL5542和ADL5320构成的增益级放大,然后发送到双工器。功率检测器用用于监测RF输出。一个单刀六掷(SP6T)开关用来选择哪一条发送或接收监测链路连接到唯一的天线。该信号链路在RF输出连接器上提供13dBm的输出功率,这符合3GPP TS25.104标准定义的发射ACLR参数。

接收链路包括声表面波(SAW)滤波器和用于监测主路径的SPDT开关。匹配模块由一个用于每个接收端口的简单串联/分流电感组成。ADF4602-1具有三个接收器输入管脚:其中一个针对频段1,另外两个分别用于高频段和低频段监测功能。频段1接收功能可能在1960MHz到2140MHz之间切换,前者用于接收上行链路信号,后者用于监测下行链路频率。ADF4602-1将选择的RF信号下变频并滤波,从而获得基带I/Q信号。AD9863中的双ADC对基带信号进行采样,并转换为数字基带的2个12位的并行码流。

这种功能划分给设计者带来了灵活性,可确保信号链路的高性能,允许选择数据转换器的速度和分辨率以适合应用要求。ADI提供的解决方案使设计者能将模拟前端与基带功能结合起来,加速毫微微蜂窝设计的面市时间,同时随着毫微微蜂窝市场的成熟,还具有能在未来整合ADI技术的好处。

ADF4602-1集成式无线收发器

图3中的ADF4602-1为3G收发器,具有无可比拟的集成度和特性组合,非常适合高性能3G毫微微蜂窝。接收器基于直接变频架构,是高集成度宽带CDMA(W-CDMA)接收器的理想选择,它完全集成了级间滤波器,从而降低了材料成本。接收基带滤波器提供了可选的带宽,可实现W-CDMA和GSM-EDGE无线信号的接收。可选的带宽以及多频段LNA输入结构使GSM/EDGE信号可作为UMTS家用基站的一部分被监测。

ADF4602-1包含两个完全集成的可编程频率合成器,用于产生发送或接收的本地振荡器(LO)信号。设计中使用了小数N分频架构来实现低噪声和快速锁定。所有必要的器件,包括环路滤波器、VCO和谐振(tank)元件都完全集成在一起以实现发送或接收合成器。VCO运行在两倍的高频频率和四倍低频频率上,使VCO在期望频率处和频率调谐范围需求内的泄漏功率最低。VCO使用多频段结构来覆盖宽的工作频率范围。设计中采用了频率和幅度校准来确保振荡器总是工作在最佳性能条件下。由于自带校准功能,可以在200微秒的PLL锁定时间内发生,因而不需要用户输入。片上VCO输出被馈入到经过调整的缓冲器级,然后再输入到正交发生电路中。经过调整的缓冲器确保在VCO传输中产生最低的电流和LO相关噪声。正交发生器产生驱动调制器和解调器所需的非常准确的调相信号。设计中采取了一些特殊的预防措施来提供发送或接收链路之间的隔离,这是频分复用(FDD)系统所要求的。

图3:ADF4602-1功能框图。

此接收器前端包括三个高性能单端低噪声放大器(LNA),允许器件支持三频段应用。其中两个适合1800MHz到2170MHz的高频段工作,而另一个适合于824MHz到960MHz。还完全集成了级间RF滤波功能,确保在混频级之前带外阻断器能恰当地进行信号衰减。单端的50Ω输入结构简化了连接处理,可减少小尺寸单端接解复用器要求的匹配元件。其卓越的线性度确保该器件能与多种SAW和陶瓷滤波器复用器一起实现良好的性能。

高线性度解调器电路被用于将RF信号变换到基带同步分量和正交分量。其中包括两个解调制器部分,它们分别针对高频段和低频段LNA输出进行过优化。高低频段输出被组合起来直接传输到基带低通滤波器的第一级,这样在基带放大之前减少了最大的强干扰信号。接收器合成器部分为VCO分布系统的混频器提供了正交LO驱动。可编程分频器允许使用相同的VCO用于高频和低频段。通过解调器和VCO分布电路的认真设计和布局,可以获得良好的90度正交相位和幅度匹配。

基带部分(包括分布式增益和滤波处理)被设计用于提供最大54dB的增益,并具有60dB的增益控制范围。通过认真的设计,通带纹波、群延时、信号损耗以及功耗都保持为最低。在制造阶段就执行滤波器校准,因而获得很高的精度和易用性。这里提供了两个可选的7阶基带滤波器:一种用于W-CDMA、截止频率为1.92MHz,另一种截止频率为100KHz,用于GSM。

在WCDMA模式中,ADF4602-1能提供102dB的增益,控制范围为90dB,分布于整个接收信号链路。RF前端包含30dB的控制范围:LNA为18dB,混频器跨导级为12dB。两个基带有源滤波器级可以提供18dB的增益控制范围,控制步进单位为6dB,因而三个12dB控制步进可以提供36dB的总增益控制范围。可变增益放大器(VGA)实现24dB的增益控制范围,控制步进为1dB。为了简化编程以及确保最佳的接收器性能和动态范围,可以简单地对总期望接收增益进行编程;ADF4602-1对增益设置进行解码,在不同模块之间自动分配增益。

发射器使用了一种创新的直接变频调制器,它具有很高的线性度和极低的噪声,同时还不需要外部发射SAW滤波器。用于I/Q信道的差分直流耦合基带接口支持从1.05V到1.4V的共模电压。允许的最大信号摆幅峰值为550mV,对应于I信道或Q信道上1.1V的差分电压范围。在正交调制器之前,基带输入信号通过截止频率为4MHz的一个2阶巴特沃斯滤波器,以抑制带外干扰。校准技术使得在整个频率范围和环境条件下维持了精确的I/Q平衡和相位,确保满足3GPP载波泄漏、EVM和ACLR要求,并且在任何条件下都有很好的性能裕量。ADF4602-1在190MHz的频率偏移下具有–163dBm/Hz的宽带背景噪声和-8dBm的输出功率,同时满足EVM和ACLR的TS25.104规范要求。输出匹配到50Ω,可实现到功率放大器的简单连接。

AD9863混合信号前端基带收发器

AD9863是针对通信市场的MxFE系列集成转换器之一,是低成本高性能毫微微蜂窝应用的理想选择。它集成了双12位模数转换器和双12位TxDAC®数模转换器。这些ADC针对50MSPS或更低采样率进行优化,工作在高达200MHz的频率下,包括一个可旁路的2×或4×的内插滤波器。该器件采用了64管脚的LFCSP封装,尺寸为9 mm × 9 mm × 0.9 mm。这里重点介绍了AD9863,但是MxFE系列(AD9860、 AD9861和AD9862)提供给设计师更多性能选择的灵活性,以及针对控制电路的辅助转换器。

图4:AD9863 MxFE框图。

市场上有各种ASIC或DSP提供一种灵活的双向24位I/O总线。在半双工系统中,接口支持24位并行传输或12位交叉传输。在全双工系统中,接口支持12位交叉ADC总线和以及一种12位交叉DAC总线。灵活的I/O总线减少了管脚数和封装尺寸。对于频分复用(FDD) W-CDMA,AD9863可以实现发送或接收信道同时工作,这需要使用全双工模式,即一条12位的交叉Rx数据总线和一个12位交叉Tx数据总线。

DAC内核将12位数据转换成两个互补的差分电流输出,并使用图5中所示的电阻网络将这些电流提供给ADF4602-1。对于1.2V的共模电压,将RDC设置为120Ω;对于1Vp-p差动输入摆幅, RL设置为63Ω。

图5:AD9863和ADF4602-1之间的简单接口。

DAC包含可编程的增益精细控制与直流偏置控制,可以用于I和Q信道之间的失配,以抑制LO馈通,并提高EVM性能。10位的直流偏置控制可以独立用于为任何一个差动管脚提供高达±12%的偏置,这样可以校准任何的系统偏置。

ADC输入由一个2KΩ差动输入电阻和一个开关电容电路组成。输入可以是针对中位电压(midsupply)的自偏置,或者可以通过编程设置来接受一个外部直流偏置。因此,建议将ADF4602-1接收基带输出直接连接到AD9863 ADC输入。ADC输入满幅电平为差分2V p-p 。

毫微微蜂窝的时钟解决方案

毫微微蜂窝需要非常准确的参考时钟(误差在±0.1 ppm),以满足3GPP规范要求。关于实现这种精确的时钟控制的方法本文不作讨论,但是值得一提的是有若干的可能性存在,包括通过监测接收器的GSM宏蜂窝同步、GPS同步以及IEEE1588精确时序协议。在某些情况下,一些毫微微蜂窝提供商也将上述方法进行组合加以实现。最终,参考时钟控制电路将控制参考频率源。在ADI的评估板上,5 这种26MHz VCTCXO用作ADF4602-1的参考时钟,延时锁相环(DLL)产生19.2MHz的时钟,是3.84MHz W-CDMA芯片时钟的几倍,此19.2MHz时钟用作AD9863的时钟输入。

AD9863提供多种时钟配置,可对很多参数进行配置。ADC时钟速度、DAC时钟速度、PLL以及内插器设置都是软件可控制的,允许针对性能来优化功率以满足要求。在推荐的配置中,PLL乘法器被设置为2×,使PLL的输出频率为38.4MHz。ADC的时钟为该频率的一半。在发送端,38.4MHz PLL的输出用于提供给DAC。发送插值被设置为2×,以抑制DAC镜像。还可能有其它的时钟频率组合。AD9863数据手册提供完整的工作模式描述。使用上述的时钟方案,毫微微蜂窝并不需要任何在宏蜂窝基站中常见的分立频率变换PLL。该器件集成了所有的频率变换功能,可帮助毫微微蜂窝满足市场要求的价格水平。

RF放大器

选择用于RF功率级的放大器为低成本、高性能宽带线性放大器,采用磷化铟镓工艺制造。这些放大器对ADF4602-1的输出进行线性放大,并弥补RF复用器和开关中的损耗。ADL5542包含内部偏置和匹配功能;ADL5320需要外部匹配,采用行业标准的塑料SOT-23封装。两种放大器都直接工作在5V的电压轨,因此不需要外部偏置电路。表1描述了放大器的关键参数。ADI的RF放大器的设计采用了专利技术,相对于电源电流具有卓越的线性度。

表1:2GHz下ADF5542和ADL5320的关键参数。

| 参数规格 | ADL5542 | ADL5320 |

| 增益 | 19 dB | 13.2 dB |

| P1dB | 18.9 dB | 25.7 dBm |

| 输出 IP3 | 37 dBm | 42 dBm |

| 噪声指数 | 3.1 dB | 4.4 dB |

| 电源电流(5V电源) | 97 mA | 104 mA |

发射输出功率与降低干扰

为了降低干扰,毫微微蜂窝必须灵活智能地设置其输出功率,以解决多个相互邻近、工作在相同频率的毫微微蜂窝的部署问题(例如在公寓内)。在这种情况下,每个毫微微蜂窝都需要以较低的输出功率发射,以避免相同频率的干扰。而且,毫微微蜂窝还不能干扰工作在邻近信道的周边的宏蜂窝基站,因为这会导致对附近连接到该宏蜂窝网络的手机产生盲点。因此要求毫微微蜂窝具有邻近信道保护功能,迫使它测试邻近下行信道的功率,根据预定义的公式来设置其功率,以便不会妨碍宏蜂窝信号。i

为使毫微微蜂窝满足要求的价格水平,并便于用户安装,这些降低干扰的技术必须是自动实现的,而不能要求某个受过训练的现场技术人员或家庭用户进行参与。当设备第一次被用户启动后,这个过程应该是自动启动的,此后每隔固定的时间段后就进行升级。ADI设计中的频段1监测接收器和ADF4602-1大的动态发射范围,允许毫微微蜂窝供应商实现自动降低干扰的技术,而不需要外部参与。监测接收器允许对邻信道的功率进行准确测试,并相应地调整输出功率。这将大约需要30dB的总发射功率动态范围。

RF性能测试

为了根据TS25.104无线系统参数规格来评估此收发器芯片组,我们将上面介绍的收发器用在评估板设计中。图6所示的评估平台使独立的发送或接收链路测试以及单独的元件测试得以实现。此评估板包括图1所示框图的功能以及功率调理。

图6:ADF4602-1/AD9863评估板。

无线电部分,包括ADF4602、AD9863、ADL5542、ADL5320和VCTCXO以及所有相关的前端开关和滤波器,占用1" × 2"的电路板面积。值得注意的是,这个电路板并没有为了节省空间尺寸而进行优化,因为它仅仅为测试而设计的,对于用作实际生产的设计可以变得更紧凑。下图包括了某些基于TS25.104参数规格的关键测试结果,这些测试结果表明了测试板上ADI芯片组的性能。

图7:频段1接收器灵敏度测试结果。

接收器灵敏度是根据接收器检测到一个低电平信号的能力来评估的,表征了接收器的噪声指数。在这次测量中采用了一个12.2KHz的参考基准。ADF4602-1的增益设置为80dB。此接收器灵敏度在整个频段超过TS25.104规格达6dB以上。

接收器的另外一个关键参数是在干扰条件下的性能。干扰测试仿真了在出现大的邻信道干扰信号条件下接收到目标信号的能力。UL 12.2kHz基准信号被设置为-101dBm,在测得的BER为10–3 时加入干扰信号。如表2所示,在所有三种情况下,ADF4602-1都以一定裕量超过TS25.104指标。

表2:接收器阻断测试结果与TS25.104参数比较。

| 接收器强干扰参数规格 | TS25.104规格极限值 | ADF4602 评估板测试结果 |

| 邻近信道选择性 | –38 dBm | –31 dBm (7 dB 裕量) |

| 10 MHz WCDMA 强干扰 | –30 dBm | –21 dBm (9 dB 裕量) |

| 20 MHz 带外 CW 强干扰 (1900 MHz) | –15 dBm | –11 dBm (4 dB 裕量) |

发射信号链路质量的关键指标为邻近信道泄漏比(ACLR)以及矢量幅度误差(EVM)。在这两种情况下,这些测试是组合发射链路线性度的关键指标。表3收集了在ADI评估板上测试的结果并与TS25.104规格进行比较。它还包括了峰值码域误差,EVM测试确保误差在码域内均衡分布。ii在所有的情况下,ADF4602-1评估板都以一定的裕量超过了TS25.104规格。图8给出了在ACLR测试中用到的输出频谱。

表3:发射器测试结果与TS25.104参数比较。

| 发射器参数 | TS25.104 参数极限值 | ADF4602 评估板测试结果 |

| 误差矢量幅度 (EVM) | <12% | 4% |

| 峰值码域误差 (PkCDE) | <–33 dB | –46 dB |

| 邻近信道(5 MHz) ACLR | <–45 dB | –49 dB |

| 间隔信道(10 MHz) ACLR | <–50 dBm | –72 dB |

图8:针对13dBm输出功率的W-CDMA频段1信号的ACLR测量结果。

图9给出了典型的毫微微蜂窝配置的发射EVM图,涉及到两个HSDPA信道以及许多语音/数据信道。复合EVM低于4%。电路评估结果表明,EVM主要是因为调制器输入处的I/Q偏置电压引起LO泄漏而产生,这是直接变频发射器的一个特点。如前面所述,这些偏置可以采用AD9863直流偏置控制进行校正。这种校正方法在应用笔记6中有完整的阐述。6

图9:典型毫微微蜂窝配置的EVM测量结果。

结束语

方兴未艾的毫微微蜂窝应用为无线电设计师在保持基站性能的同时将成本降至最低带来了特有的挑战。ADI 3G毫微微蜂窝芯片组由集成了无线收发器的ADF4602-1、MxFE基带收发器AD9863和ADL5542、ADL5320RF放大器组成,该芯片组使设计师能以紧凑的外形尺寸满足TS25.104规格要求。

参考文献

1www.analog.com/AD9863

2www.analog.com/zh/rfif-components/rfif-transceivers/adf4602-1/products/product.html

3www.analog.com/ADL5542

4www.analog.com/ADL5320

5ADF4602 and AD9863 Femtocell Evaluation Board, EVAL-ADF4602EB1Z Data Sheet.

6Transmit EVM Calibration on the ADF4602 W-CDMA Transceiver. AN-xxx

iTSG R4#48 - TSG-RAN Working Group 4 (Radio) meeting #48 October 2008.

iiTSG R4#8 (99)705 - TSG-RAN Working Group 4 (Radio) meeting #8. October 1999.

作者简介

Thomas Cameron (thomas.cameron@analog.com) 于2006年加入ADI公司。目前是一位专注于无线基础设备市场的技术业务经理,他于1986年加入Bell Northern Research(现今的北电网络)公司无线网络部门,曾担任多个职位,涉及电信网络技术、设备和子系统研究、设计和管理。1999年他加入Sirenza Microdevices公司,升任为无线产品行销总监。2004年,他加入WJ Communications公司,担任欧洲销售经理一职。Thomas拥有加拿大沃特卢Wilfrid Laurier大学理学学士学位、加拿大渥太华Carleton大学工程硕士学位和乔治亚理工学院电气工程博士学位。他拥有7项专利,撰写过大量的技术论文和文章。

Peadar Forbes (peadar.forbes@analog.com) 于2004年毕业于爱尔兰科克大学,获得微电子工程理学学士,随后加入ADI公司。目前他从事与RF产品线有关的工作,提供RF收发器和PLL产品的应用支持。在业余时间内,Peadar喜欢听音乐、弹吉他、运动和旅游。

粤公网安备 44030902003195号

粤公网安备 44030902003195号