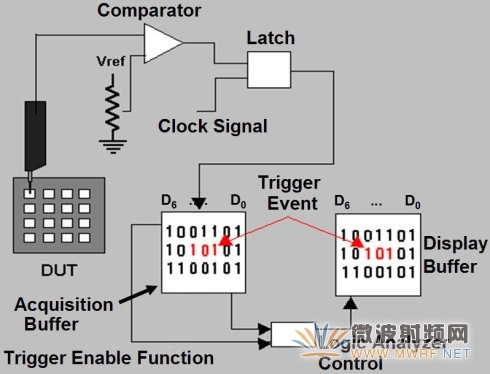

逻辑分析仪是常用的电子仪器之一,主要应用于做数字电路测试,FPGA调试,CPU/DSP调试,数字IQ/IF分析,无线通信/雷达接收机测试等场合。逻辑分析仪由模块和计算机组成(当然还有探头),模块负责数据的触发,采集和存储的工作,计算机负责后端的数据显示,数据处理和分析等工作。图1是典型的逻辑分析仪模块图。

图1

逻辑分析仪模块包括如下几个部分:

1)探头连线:连接探头把信号引入到模块内部;

2)信号调理:信号的放大和对比(和门限电压对比);

3)信号采集:由外部时钟或内部时钟进行信号的采集;

4)触发电路:执行信号的模拟和逻辑触发;

5)内存控制器:管理存储器。

逻辑分析仪有两种分析模式:定时模式和状态模式。

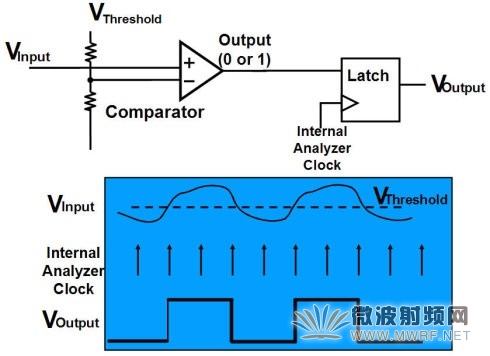

图2是定时模式的采集原理。定时模式的采集由逻辑分析仪内部时钟执行,是异步采集,适合于查看多通道信号的时序关系。

图2

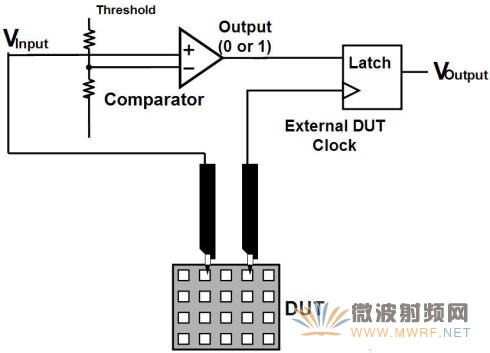

图3是状态模式的采集原理。状态模式的采集由外部输入时钟执行,是同步采集,适合于数据捕获,协议分析和处理器调试等应用。这是逻辑分析仪独特的能力。

图3

整个逻辑分析仪的结构框图如图4所示。

图4.逻辑分析仪结构框图

作者:安捷伦科技专家 孙灯亮

粤公网安备 44030902003195号

粤公网安备 44030902003195号