近日,电子科技大学电子科学与工程学院(示范性微电子学院)博士生张净植在2018年国际固态电路会议(ISSCC)上发表论文,提出了一种“基于强耦合变压器的电流提升技术”,并在此基础上研发了一款芯片实现了多个频段全部覆盖,让5G“全球通”变成了可能。

△ ISSCC大会主席、MIT教授Anantha Chandrakasan(右)和多伦多大学教授Kenneth C. Smith为张净植颁发 “Silkroad Award” 奖牌

张净植为论文第一作者,其导师康凯教授为论文通讯作者,电子科技大学为唯一作者单位。据了解,该论文是中国大陆地区发表在该会议上的首篇有关毫米波集成电路设计的论文,为我校首次以第一作者单位在该会议正文单元上发表的论文。

张净植同时获得该会议颁发的“Silkroad Award”,该奖项是颁发给以第一作者身份第一次在这个会议上发表论文的亚太地区的学生。张净植成为中国大陆地区历史上第4位获此殊荣的学生,同时也是大会历史上第20位获此奖项的学生。

“通用芯片”:解决“5G时代”的新问题

张净植研发的这款芯片,源于三年前的偶然发现。2015年,康凯教授正承担国家5G技术方面的重大专项,张净植有机会参与其中,负责其中关于频率源的部分研究任务。

在4G时代,各个国家所用的频段都在3GHz以下,不少手机生产商采用了多个芯片来覆盖所有频段,并且在频率较低的情况下,器件性能好,即使用一个芯片来覆盖所有频段,设计也相对比较简单。而到了5G时代,不同的国家划分的应用于5G通信的频段大大提高,中国用的是24.75-27.5GHz和37-42.5GHz频段,美国用的是27.5-28.35GHz、37-38.6GHz和38.6-40GHz频段,欧洲用的是24.25-27.5GHz频段,日韩则采用26.5-29.5GHz。而同一个手机要支持这么多不同的高频段,则相对困难,这可能就会导致我们出国旅游时手机无法正常通信。

那么问题来了,究竟能否研发一款宽频带“通用芯片”全部覆盖以上各个不同的高频段呢?

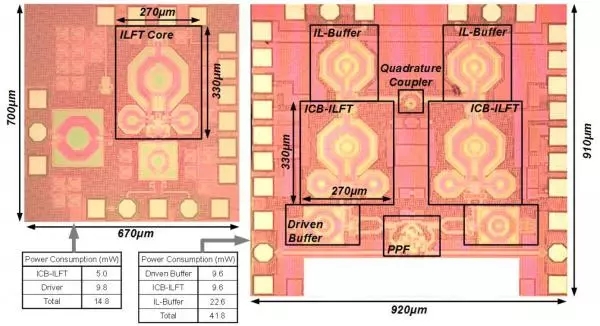

答案是肯定的。张净植在国际固态电路会议展示的研究成果,就是两方小小的“通用芯片”:大的芯片只有910微米×920微米(1微米=10-6米),小的芯片为700微米×670微米,面积都小于1平方毫米,大小相当于一根针的横截面。

△ 左边是差分输出芯片,是核心电路的验证模块;右边是正交输出芯片,是完整的、可以用于5G系统的芯片。

这种小芯片却具有“兼容并蓄”的广阔“胸怀”,极大地提升了注入锁定倍频器的工作带宽。它的专业称呼是“基于CMOS(互补金属氧化物半导体)工艺的超宽带注入锁定倍频器”,简而言之,就是为了解决5G芯片在不同电磁频段“水土不服”的难题而专门设计的。

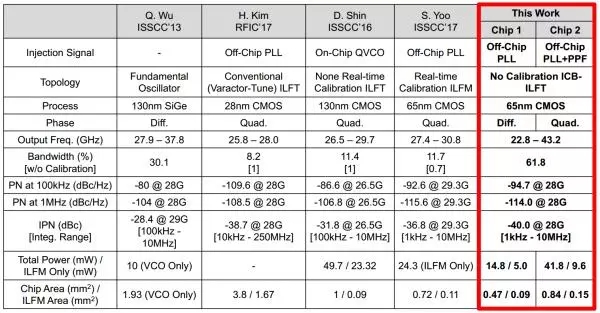

在与业界最先进技术的比较中,该技术在仅消耗两倍功耗的情况下,将工作带宽提升了5.2倍。它还解决了毫米波频段中“低相位噪声信号源的大带宽设计”挑战,为毫米波领域超宽带低相位噪声信号源设计提供了一个可行方案,对5G通信的高频段多频带应用有着实际意义。

历时三年:过程一波三折

从2015年萌生想法到2016年9月真正开始设计,张净植尝试了多种思路。他首先想到,输入电流和工作带宽是正相关的,如果要提高电路的带宽就得想办法增强输入电流。而要增强输入电流,一种方法是增大输入信号,但一般而言,外部给的输入信号大小是固定的,所以此路不通。还有一种方法,就是提高输入极的增益,但业界已经把输入极优化得很好,想进一步提升基本不太可能。

在不断提出问题又不断自我否定之后,张净植提出了一个突破性的想法:能不能用无源电路把电流提升,然后插入一个变压器,这样就可以使电流提高N倍同时能把带宽也提高N倍呢?又经过三个月的努力,他和团队在2016年12月份完成芯片设计并进行了第一次流片。

2017年3月,终于拿到芯片。测试的结果令他非常激动:和2017年国际国内最新的研究成果相比,他们的研究已经在性能上远远胜出。此前,业界做出的芯片工作带宽大概在10-30%,而他们的芯片带宽可以达到60%以上。于是,他和康凯教授商量,很有必要再次优化设计并做第二次流片。

芯片优化设计的时间十分紧凑:做芯片一般要依次完成原理图、版图、模块级联,最后才是完成总版并进行评估,但到了2017年4月,他们才刚做到模块级联环节,进度比预期慢很多。考虑到芯片设计不容有失,否则流片就会功亏一篑,他们决定不能急于求成,最终到5月才完成第二版设计。

由于芯片造价成本高昂,而且准备第二次流片时没有项目支撑,他们经过许多周折,向国内外其他单位寻求支持。第二次流片终于结束,但在过海关时却卡了很久,直到8月底才拿到第二版芯片。他们快速行动,花了一周时间测试芯片的性能,然后快速写论文投给了国际固态电路会议。10月,国际固态电路会议给出了评审意见。团队成员终于松了一口气:总算没有失之交臂!

△ 右边两栏为该论文达到的工作指标,其中,带宽为22.8-43.2GHz,积分相位噪声为-40.0dBc,功耗为5.0mW。与业内同类工作对比,该成果的带宽达到了其他工作的5.2倍,同时没有带来相位噪声的恶化。

肯吃苦、多拼搏,为行业做更多贡献

2018年2月,国际固态电路会议召开。该会议是目前国际公认集成电路领域的权威会议,有着“Chip Olympics(芯片奥林匹克)”的雅称,自1954年成立以来,共发表相关学术论文7500余篇。中国大陆地区作者于2005年发表首篇论文,截至目前在该会议上发表的相关文章有24篇。

此前,我校硕士生郭开喆、余益明同学(原电子工程学院)和本科生周雄同学(原通信与信息工程学院)的论文曾入选该会议“学生科研前瞻”单元汇报展示。如今,张净植再次创造历史,并与来自日本北海道大学的博士生Kodai Ueyoshi共同获得大会为亚太地区的优秀学生论文设立的“Silkroad Award”奖项。

对于这次研究成果,张净植十分感激康凯教授及团队的大力支持。他说,集成电路不同于其他学科,每一次设计完成以后拿出去加工,就没有改正的机会了。每一次流片的成本都非常大,设计过程中的任何一点小失误,都可能导致全盘皆输。正是康凯教授和团队在芯片设计方面的悉心指导和严格要求,以及对流片工作的大力支持,才使他有机会参与到这项重要的研究工作中来,并取得了一定的成绩。

张净植表示,“做这一行非常累,要做好足够的心理准备,熬夜也是常有的。只有肯吃苦、肯拼搏,才能为这个行业做出更多贡献!”目前,团队正在进一步优化设计,准备做第三版设计和流片工作。他说,“我们的芯片设计从一开始就是面向应用并且和工业界紧密结合的,随着5G通信时代的到来和各种应用逐渐推广,我们的芯片也可能会进入产品化阶段,应用到手机和基站,让5G也可以实现‘全球通’”。

粤公网安备 44030902003195号

粤公网安备 44030902003195号