| 资料语言: | 简体中文 |

| 资料类别: | PDF文档 |

| 浏览次数: | 0 |

| 评论等级: | |

| 更新时间: | 2015-08-20 00:18:32 |

| 资料查询: |

在一个电子系统中,印制板作为硬件系统的核心部件之一,印制板设计的好坏将直接影响到整个系统的稳定性,因此,在设计之初就充分考虑到电磁兼容的问题,考虑到信号的完整性等,无疑将提高系统的稳定性,缩短开发周期,提前将稳定的系统推向市场。

目 录

目 的 ·· 11

范 围 ·· 11

定 义 ·· 11

引用标准和参考资料 ··· 11

指导书内容 ··· 12

第一部分 层的设置 · 12

1 层的设置 12

1.1 合理的层数12

1.1.1 Vcc 、 GND 的层数 · 12

1.1.2 信号层数 ··· 13

1.2 电源层、地层、信号层的相对位置···13

1.2.1 Vcc 、 GND 平面的阻抗以及电源、地之间的 EMC 环境问题 · 13

1.2.2 Vcc 、 GND 作为参考平面,两者的作用与区别 · 13

1.2.3 电源层、地层、信号层的相对位置 ·· 14

第二部分 布线 · 19

2 布线 ··· 19

2.1 布线基本规则··19

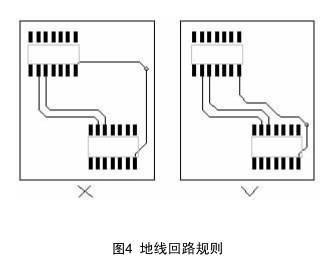

2.1.1 地线回路规则 ··· 19

2.1.2 窜扰分析与控制规则 19

2.1.3 走线屏蔽规则 ··· 20

2.1.4 走线的方向控制规则 20

2.1.5 走线的开环检查规则 20

2.1.6 阻抗匹配检查规则 21

2.1.7 走线终结网络规则 21

2.1.8 走线闭环检查规则 22

2.1.9 走线的分枝长度控制规则 22

2.1.10 走线的谐振规则 ·· 22

2.1.11 走线长度控制规则 ·· 22

2.1.12 倒角规则 · 23

2.1.14 器件布局分区 / 分层规则 24

2.1.15 孤立铜区控制规则 ·· 24

2.1.16 PCB 板层定义规则 ··· 24

2.1.17 电源与地线层的阻抗匹配规则 ·· 25

2.1.18 重叠电源与地线层规则 ·· 25

2.1.19 3W 规则 · 25

2.1.20 20H 规则 ··· 26

2.1.21 五一五规则 · 27

2.1.22 低速电路 · 27

2.1.23 转角走线 · 28

2.2 串扰 ·28

2.3 优选布线层··29

2.3.1 布线层的优先级别 ·· 29

2.4 阻抗控制30

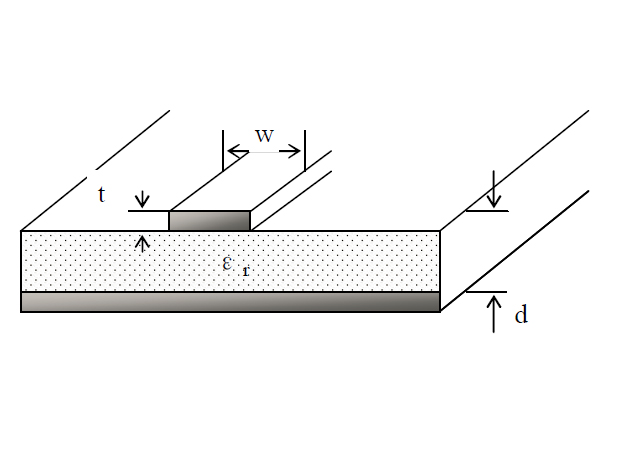

2.4.1 输入阻抗 · 30

2.4.2 特征阻抗 · 31

2.4.3 屏蔽地线对阻抗的影响 ·· 31

2.5 跨分割区及开槽的处理 ··31

2.5.1 对电源/地平面分割造成的开槽 32

2.5.2 通孔过于密集形成开槽 ·· 32

2.5.3开槽对PCB板EMC性能的影响 32

2.5.4 对开槽的处理 · 36

第三部分 地回路设计 ··· 39

3 地回路设计 · 39

3.1 地的分割与汇接··39

3.2 接地的含义··39

3.3 接地的目的··39

3.4 基本的接地方式··39

3.4.1 单点接地 · 40

3.4.2 多点接地 · 40

3.5地线回路导致的电磁干扰 ··41

3.6 接地和信号回路(涡流除外)·42

3.7 浮地 ·42

3.8 关于接地方式的一般选取原则·42

3.9 单板接地方式··42

第四部分 典型电路的PCB 设计 44

4 典型电路的PCB 布局 44

4.1概述·44

4.2功率主电路的PCB EMC布局原则 ·44

4.2.1 PCB 辐射原理分析 · 45

4.2.2 PCB EMC 布局原则 ·· 46

4.3 PFC电路的布局··49

4.3.1 PFC 电路噪声源的形成 · 50

4.3.2 PCB 布局的对策 · 50

4.4单端正激电路··51

4.4.1 主电路拓扑图 · 51

4.4.2 噪声源的形成与 PCB 布局对策(以 AVH30 为例) 55

4.5单端反激电路··56

4.6 非隔离电路(正激)56

4.7 双正激电路57

4.7.1 主电路拓扑图 · 57

4.7.2 噪声源的形成 ··· 58

4.7.3 PCB 布局的对策 · 58

4.8 全桥电路59

4.8.1 主电路拓扑图 ··· 59

4.8.2 噪声源的形成 ··· 60

4.8.3 PCB 布局的对策 · 61

4.9 半桥逆变电路62

4.9.1 主电路拓扑图 ··· 62

4.9.2 噪声源的形成 ··· 62

4.9.3 影响半桥逆变电磁噪声的其他因素 63

4.9.4 PCB 布局的对策 · 64

第五部分 电源EMI 滤波器的PCB 设计 ··· 66

5 电源EMI 滤波器的PCB 设计 66

5.1 概述 ·66

5.2 EMI滤波器的基本结构···66

5.3 布局考虑66

5.3.1 输入线与输出线的布置 66

5.3.2 多级滤波器级联 67

5.3.3 EMI 滤波器的位置 · 67

5.3.4 共模 / 差模电感的布置 ·· 67

5.3.5 三相 EMI 滤波器的线圈布置 · 68

5.3.6 电容的布置 · 68

5.4 布线考虑68

5.4.1 电容的引线最短 68

5.4.2 电容的引线开槽 ·· 68

5.4.3 接地线设计 ··· 69

5.4.4 接地螺钉孔设计 ··· 69

图表说明

图1 四层PCB的主选层设置方案15

图2 四层板解决方案2·15

图3 四层板解决方案3·16

图4 地线回路规则···19

图5 窜扰分析示图···19

图6 走线屏蔽规则···20

图7 走线的方向控制规则···20

图8 走线的开环检查规则···21

图9 防天线效应的布线规则图21

图10 走线终结网络规则·21

图11 走线闭环检查规则·22

图12 走线的分枝长度控制规则··22

图13 走线的谐振规则·22

图14 走线长度控制规则·23

图15 倒角规则·23

图16 器件去耦规则·23

图17 器件布局分区/分层规则 24

图18 立铜区控制规则·24

图19 PCB板层定义规则···25

图20 电源与地线层的阻抗匹配规则··25

图21 重叠电源与地线层规则 ·25

图22 3W规则26

图23 电源平面的RF辐射 26

图24 数字、模拟区边界线使用20H规则···27

图25 树状布线图·27

图26 直角转弯走线·28

图27 PCB板上的串扰···28

图28 输入阻抗·31

图29 通孔密集形成开槽·32

图30 低速信号的回流电流路径分布··33

图31 高速回流信号回流电流路径分布··34

图32 地平面开槽引起信号间的串扰··35

图33 当跨分割走线不可避免时应该进行有效的桥接···37

图34 接插件不能安装在地层隔逢上··37

图35 高密度接插件的处理 ·38

图36 单点接地示意图·40

图37 公共地阻抗耦合·41

图38 隔离变压器的地分割图 ·43

图39 差模回路形成的环形天线辐射··45

图40 共模不平衡偶极子天线 ·46

图41 设置镜像平面减小地线电感··47

图42 由镜像理论(a)轨线及导电平面可等效为(b)四个PCB轨线48

图43 与地回路连接的一根电缆及其作为一个非平衡偶极子天线的等效电路图49

图44 PCB轨线下放置导电平面,有效降低电缆的辐射示意图 49

图45 PFC电路拓扑···50

图46 单端正激电路拓扑图 ·52

图47 输入主回路的局部电路图··52

图48 输出整流回路的局部电路图··52

图49 A点实际工作时典型波形图53

图50 图中B点实际工作波形图···53

图51 图中C点实际工作波形图···54

图52 变压器副边两端的电压波形··55

图53 原边为RCD复位的电路图 ·55

图54 单端反激电路·56

图55 AVN40(非隔离电路)主功率电路图 ··57

图56 双正激电路拓扑图·57

图57 双正激电路器件原边布局··59

图58 双正激电路器件副边布局··59

图59 全桥电路主电路拓扑图 ·60

图60 全桥电路原边布局图 ·61

图61 全桥电路副边布局图 ·62

图62 半桥逆变电路布局·64

图63 EMI滤波器的基本结构···66

图64 EMI滤波器的输入线与输出线布置67

图65 EMI滤波器的位置···67

图66共模/差模电感的布置··68

图67 电容的引线最短·68

图68 电容引线的开槽·69

图69 接地线设计·69

表- 1 四层板解决方案表.... 14

表- 2 六层板解决方案表.... 16

表- 3 八层板解决方案表.... 17

表- 4 十层板解决方案表.... 17

表- 5 12层板解决方案表..... 18

表- 6 不同条件下的串扰... 29

温馨提示:本站不提供资料文件下载,仅提供文件名称查询,如有疑问请联系我们。

粤公网安备 44030902003195号

粤公网安备 44030902003195号