| 资料语言: | 简体中文 |

| 资料类别: | PDF文档 |

| 浏览次数: | 0 |

| 评论等级: | |

| 更新时间: | 2013-01-08 14:52:24 |

| 资料查询: |

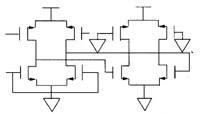

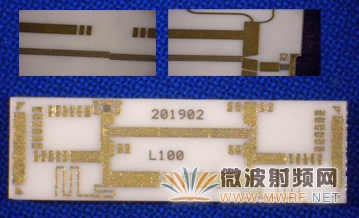

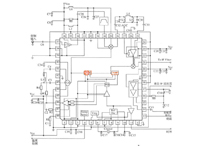

提出了一种基于高速锁存器的CMOS高速分频器结构,阐述了其工作速度,工作范围,前后级级联电路设计。采用典型的TSMC 0.18 um/1.8 V工艺模型,通过Agilent的ADS进行模拟验证,得到其最高工作速度为12 GHz,工作范围为3~12 GHz,在6~12 GHz内,输入灵敏度不小于100 mV,功耗小于28 mW。

温馨提示:本站不提供资料文件下载,仅提供文件名称查询,如有疑问请联系我们。

粤公网安备 44030902003195号

粤公网安备 44030902003195号