温度的变化会导致高频电路性能的变化。不管这些温度变化是来自电路本身的内部散热,或者是安装在电路上的设备,又或者是来自于外界环境,它们可能会对电路的性能产生影响。例如,越来越多的汽车配备了基于毫米波电路的先进驾驶辅助系统(ADAS),以避免发生碰撞。幸运的是,表征电路材料特性的介电常数温度系数(TCDk)为设计人员提供了一种方法,可让其了解材料的介电常数Dk(相对介电常数或er) 随温度变化的关系。当电路板必须安装在温度变化很大的环境中,例如在汽车电子产品或5G基站,该参数可以用来预测电路材料在毫米波频率下的性能公差。

射频/微波印刷电路板(PCB)中的温度变化可能由多种因素引起。当电路从通电到断开的过程中,电路的工作周期会发生温度变化,从而导致性能变化。PCB材料的厚度是需要考虑的这些因素之一。相比较而言,较薄的PCB电路的RF性能对导体效应更为敏感。相反,较厚电路对介质更为敏感。通常情况下,导体效应影响高频电路的插入损耗,而电路的介电特性会影响电路的相位响应等。无源元件如滤波器和功分器的插入损耗至关重要,而相控阵天线则更关注于相位响应,也就是PCB的介电特性。但也有例外的情况。

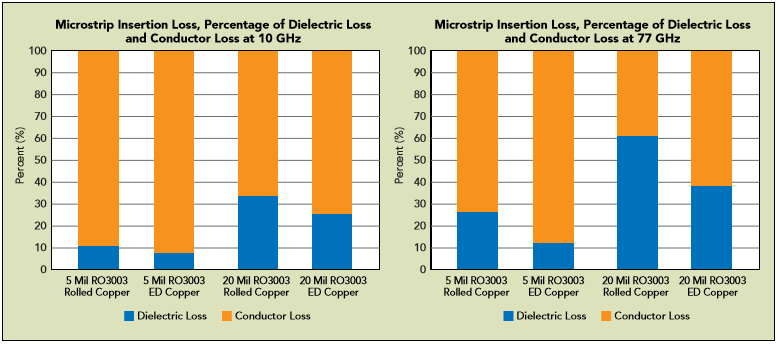

如图1所示,插入损耗是介质损耗、导体损耗、辐射损耗和泄漏损耗四种损耗成分的总和。在此示例中,泄漏损耗和辐射损耗已被忽略。对于大多数高频材料的PCB电路来说,泄漏损耗通常不是问题,因为这些材料具有非常高的体电阻率。尽管高功率应用可能会有例外,本文这里先不做讨论。图1中也没有考虑辐射损耗。辐射损耗主要与电路设计有关,许多变量会影响电路的辐射损耗。图1主要是帮助读者了解导体效应对薄电路和厚电路的影响。

图1、不同材料厚度的50欧姆微带传输线电路的插入损耗中介电损耗和导体损耗所占百分比

可以看出,对于图1中的50Ω传输线电路,导体效应对于较薄电路的影响更为显著,反过来介电效应对于较厚电路影响更大。为什么需要了解这些呢?因为随着低频带宽的消耗以及越来越多毫米波电路应用,在毫米波频率下PCB更多使用薄的电路材料。此时,电路设计者应该关注导体效应,它包括是由铜表面粗糙度和导体的最终表面处理引起。

通常在较低的频率下使用较厚的电路材料:最小化导体效应,但介电效应增加。介电效应主要是指电路中的介质材料和任何非金属的耗散因子。其中的非金属的耗散因子是诸如在电路中添加的非金属的阻焊层和防护涂层,它们会影响介质损耗。图1比较了薄电路(5mil厚度)和较厚电路(20mil厚度)的损耗性能中各自所占不同损耗的比重差异。当然20mil在某些应用中并不被认为是厚的,但越厚电路介质损耗更占主导的作用。例如,对于30mil厚的电路,介质损耗将更加显著,而60mil厚的电路插入损耗将几乎以介质损耗为主。

理解基于电路材料厚度的变化对电路性能的影响让我们更好的了解在不同频率下PCB厚度的选择,而且也可以更好的理解TCDk对电路的潜在影响。理论上,较厚电路应该更容易受TCDk的影响,因为TCDk是一种介电特性。但是,由于电路在不同温度下工作时,其铜电导率也会略有变化,而这些变化也可能导致基于薄的射频电路比厚的射频电路性能变化更加明显。

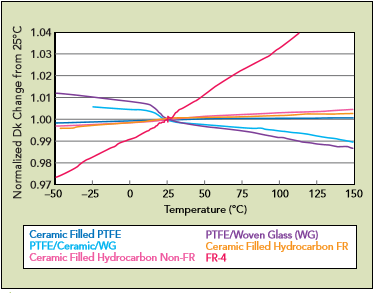

尽管不同材料的配方不同,其由温度变化引起的Dk变化量可能有很大差异,但所有电路材料都具有TCDk特性。图2介绍了几个不同配方体系的电路材料的TCDk变化曲线。

图2、几种不同体系的电路材料的TCDk曲线

这些TCDk曲线的数据是通过测试原始PCB介质材料得到的,而非加工的电路。测试方法采用是IPC-TM-650 2.5.5.5c定义的X波段夹紧式带状线谐振器法,测试频率是10GHz。我们评估了多种具有不同TCDk特性的PCB材料。其中棕色曲线是FR4材料,其通常不被用于高频率电路中。它的TCDK特性非常差,且FR-4的配方几乎也不具有良好的TCDK性能。紫色曲线显示在室温附近其TCDk有显著的变化,这是PTFE树脂的本质特性。这条曲线是仅仅是PTFE树脂和玻璃布增强的材料。但是,当陶瓷填料添加到配方中(浅蓝色曲线)时,室温下的TCDk变化就会大大降低。

深蓝色曲线表明,并非所有的陶瓷填料都是相同的,理解陶瓷工程的复杂性可以有所作为的。这条深蓝色曲线正是诸如RO3003™电路材料的TCDk曲线。RO3003™是一种陶瓷填充的、无玻璃布的PTFE材料,TCDK为-3ppm/℃。由于特殊的陶瓷填料,室温下的TCDk无明显变化。理想情况下TCDk应该是0ppm/℃,即Dk不随温度的变化而变化。作为数字参考,TCDk小于|50|ppm/℃或更低可认为较好。之所以使用绝对值是因为一些材料的TCDK具有负斜率趋势,一些材料具有正TCDK斜率。作为参考,品红色曲线的TCDK为50ppm/℃。

尽管图2所示的图表有助于理解材料的TCDK性能,但由于该测试方法的原因,它仍然具有多方面局限性。一方面是测试频率受到限制,另一方面是测试未使用实际电路。罗杰斯公司开发了一种测试方法,可以评估不同温度下的电路Dk变化,被称为电路TCDK测试法。它通过使用特殊装置的微带差分长度法去评估某一温度下的电路特性。

电路TCDk测试方法如下:在被评估的材料上制作两个50Ω微带传输线路电路,除了物理长度外其它都是相同的。一个电路是2英寸,另一个是8英寸。首先将电路放在加热装置上,此时并不加热而使其处于室温,测试初始室温下的射频性能。获取初始室温数据后,打开加热块并把温度调整到某一温度,如65°C。当电路达到这个温度仍保持一段时间以确保达到温度的热平衡,可通过安装在电路旁的热电偶和FLIR®热成像摄像机对其进行监视。电路在该温度下稳定后,就可以进行测试扫描并捕获数据了。接下来,继续调整加热装置使温度升高,比如125°C,再次达到热平衡后继续测试并收集数据。2英寸的电路和8英寸电路均通过相同的步骤进行测试。本文并不涵盖这种测试方法的许多细节,如果需要详细信息请联系罗杰斯公司。

罗杰斯公司评估了多种不同材料的电路TCDk特性,但这里仅就其中两种材料的比较作为电路TCDk的介绍。为了更好的了解TCDk对电路性能的影响,分别对较差的TCDk和较好的TCDK性能材料进行比较。通过评估不同基板厚度和不同铜类型的材料,可以了解TCDk对射频性能的影响是否因基片厚度或铜类型的不同而有所不同。

测试

本次选用的高频材料为RT/Duroid®5880和RO3003™层压板。RT/Duroid5880材料作为市场上推出的损耗最低的电路材料之一,有着良好的、悠久的历史,尽管它有着125 ppm/°C的差的TCDk。RO3003材料已经应用于不同领域多年,并且已经成为了77GHz汽车雷达传感器的首选材料。RO3003材料的TCDk为-3ppm/°C。本次研究的PCB板厚度选用5mil和10mil,使用的压延铜和标准电解铜箔。压延铜的平均表面粗糙度为0.35μm RMS,而标准电解铜的平均表面粗糙度为2.0μm RMS。

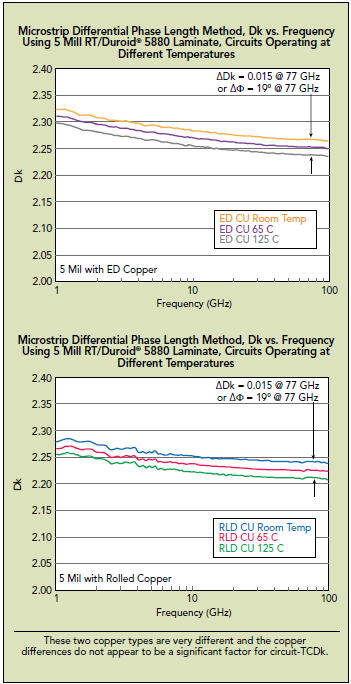

图3给出了在使用5mil RT/duroid 5880®层压板,采用压延铜和标准电解铜制成的电路的TCDk测试结果。

图3、比较了不同温度下,略差TCDk的介质材料采用不同铜箔类型的电路TCDk

图3显示在不同的温度下,铜箔类型几乎不会引起电路TCDk性能差异。实际这两种铜箔的晶体结构非常不同,导电率非常相似,但是不同温度变化引起的导电率的差异似乎并不明显。需要注意,这里比较的基于该材料两种不同铜箔类型的电路时,得到的Dk的偏移(即图表y轴上的数据)是属于正常偏移。电磁波在粗糙的标准电解铜会比光滑的压延铜中的传播更慢,而对应的相速较慢会导致有效介电常数和最终得到的材料Dk增大。罗杰斯公司称最终得到的材料的Dk为设计Dk。

为了继续进行有关TCDk的研究,仍使用相同材料同类型铜箔,但不同厚度,去评估温度对不同厚度的电路材料TCDk的影响。图4是77 GHz下测量评估的结果。

图4、比较了不同温度下,具有略差TCDk的相同材料、相同铜箔,但不同厚度的电路TCDk

如图4所示,电路TCDk的变化差异与材料厚度相关。与较薄电路相比,较厚电路的设计Dk随温度变化差异更大。在不同的工作温度下,由于材料的TCDk而引起的Dk的变化表明,较厚电路材料对介质性能的影响要大于对导体性能的影响。

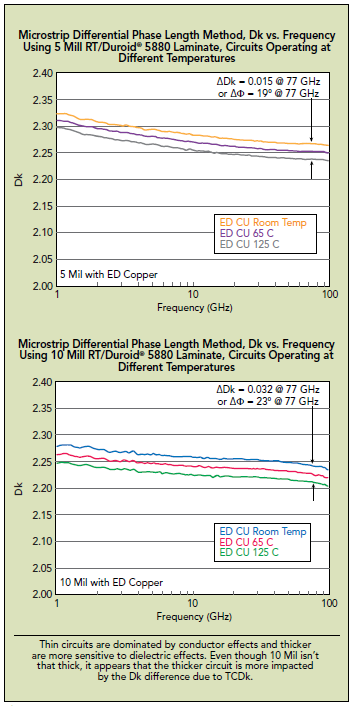

图5显示了使用具有较好TCDk性能的材料进行电路TCDk 测试的结果。如图 所示,使用具有较好TCDK材料,不同铜箔类型的电路的Dk随温度变化上几乎没有差异。图3也显示了在使用较差TCDk的材料时,不同铜箔类型不会影响电路的TCDk。通过比较,很明显看到使用较好TCDk 性能材料的电路Dk或相角的随温度的变化差异最小,而使用较差的TCDk性能材料的电路随温度变化就大很多。

图5、比较了不同温度下具有较好TCDk的相同厚度材料,采用不同铜箔类型的电路TCDk

另一个与温度有关的介质材料特性,即介质损耗温度系数(TCDf),也可能受到电路材料的相对厚度的影响。但由于常规测试方法的局限性,该TCDf很难准确测量。例如,诸如IPC夹紧式带状线谐振器测试方法就对组成测试夹具的金属非常敏感。当金属在不同的温度下膨胀和收缩时,这就导致了测试方法的不准确性。另一个方面,通过这种测试方法提取Df时,也存在测试样品的类型以及不同类型对温度变化引起的物理尺寸的敏感变化的问题。而且,测试方法中谐振片的导体由于温度变化引起的电导率也会发生变化。尽管铜导体电导率的变化非常微小(可能一个很小的值),但是考虑到Df的计算提取过程中材料介质损耗以及其它损耗(导体损耗和辐射损耗)本身就非常敏感的特性,那么由于温度变化引起的铜导体电导率的微小变化也会导致Df提取准确度问题。

更为现实的方法可以通过测试电路在不同温度条件下的插入损耗来评估材料由于温度产生的损耗变化。作为电路TCDk实验的一部分,对电路的其它性能也进行了评估。与Dk 变化相关的电路其他特性,如相位响应和阻抗,与Dk随温度的变化趋势是非常相似的。当然,电路的插入损耗,特别是不同温度下的插入损耗也进行了测试。 图6比较了5-mil RT/duroid®5880层压板材料使用不同类型铜箔时的电路的插入损耗随温度的变化情况。图中曲线所表示的电路插入损耗随温度变化的测试是与电路TCDk的测试所使用的被测电路相同,且同时收集了数据。

图6、比较了使用5mil RT/duroid® 5880层压板的两种不同类型铜箔的电路在不同温度下的插入损耗变化

如图6所示,铜箔表面粗糙度对这些电路的损耗影响是非常明显的。压延铜具有非常光滑的铜箔表面,对导体损耗的影响较小,从而对插入损耗的影响也很小;而铜箔表面粗糙的标准电解铜对损耗的影响较大。在5mil RO3003™层压板上测试的损耗趋势类似于图6所示的结果,这里先不做讨论。进行不同温度下插入损耗测试主要是比较较差TCDk材料和较好的TCDk材料,看是否较差的TCDk材料它的TCDf较差,或随温度变化的Df变化很大;而较好的也较好。不幸的是,由于这些材料(RT/duroid® 5880和RO3003™层压板)具有非常低的损耗因子(Df 0.001或更低),电路损耗随温度和频率变化而变化并不明显。

使用更高损耗的材料进行的类似比较,它们分别具有较好和较差TCDk,期望能够得到较差TCDk的材料也将具有较差TCDf。然而,这个实验更为复杂,因为不同的材料配比随温度变化而表现出不同结果。基于PTFE材料的可能与大多数基于烃的材料有很大不同。而且,不同的PTFE材料的性能可能会因所使用的填料不同、以及用于层压板的玻璃布类型或玻璃布的用量不同而有所差异。

总而言之,所有的电路材料都具有TCDk的固有属性,它是任何可能处于不同温度环境下的应用电路在设计阶段都应考虑的重要参数。电路板的厚度会影响电路的性能。随着温度的变化,较厚材料的电路可能会因为材料TCDk参数使Dk变化更大。在研究中由于受到铜箔类型少的限制,铜箔引起的差异似乎并不明显影响TCDk电路性能。此外,如图3、4和5所示,电路材料的TCDk与频率无关。尽管可能看到很小的差异,但是从10GHz至77 GHz范围内Dk偏移量大致相同。数据手册中的TCDk值通常在10GHz下进行测试的,而且是用于没有铜箔的纯介质材料。当考虑电路形式的TCDk效应时,可以看到材料的厚度会影响TCDk且对电路性能的影响。这表明,当设计人员进行电路仿真时,应根据原始介质材料的Dk在温度范围内可能发生的变化,多尝试采用不同Dk值进行仿真。以便更好地了解Dk的温度变化对电路的影响。

参考文献

1. John W. Reynolds, P.A. LaFrance, J.C. Rautio and Al F. Horn III, “Effect of the Conductor Profile on the Insertion Loss, Propagation Constant, and Dispersion in Thin High Frequency Transmission Lines,” DesignCon 2010.2. John Coonrod, “Insertion Loss Performance Differences Due to Plated Finish and Different Circuit Structures,” APEX / IPC Expo 2019, Feb. 2019.

3. John Coonrod, “Characterizing Circuit Materials at Millimeter-Wave Frequencies,” Microwave Journal, Vol. 62. No.5, May 2019.

更多技术文章,欢迎登录“罗杰斯技术支持中心”查看。

粤公网安备 44030902003195号

粤公网安备 44030902003195号